# DIFFERENTIAL CODE-SHIFTED REFERENCE IMPULSE-RADIO ULTRA-WIDEBAND RECEIVER: TIMING RECOVERY AND DIGITAL IMPLEMENTATION

by

Khalid Aldubaikhy

Submitted in partial fulfilment of the requirements for the degree of Master of Applied Science

at

Dalhousie University Halifax, Nova Scotia June 2012

© Copyright by Khalid Aldubaikhy, 2012

## **D**ALHOUSIE **U**NIVERSITY

#### Department of Electrical and Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Graduate Studies for acceptance a thesis entitled "Differential Code-Shifted Reference Impulse-Radio Ultra-Wideband Receiver: Timing Recovery and Digital Implementation" by Khalid Aldubaikhy in partial fulfilment of the requirements for the degree of Master of Applied Science.

|                 | Dated: | June 26 <sup>th</sup> , 2012 |

|-----------------|--------|------------------------------|

| Co-Supervisors: |        |                              |

|                 |        |                              |

|                 |        |                              |

|                 |        |                              |

| Readers:        |        |                              |

|                 |        |                              |

|                 |        |                              |

# Dalhousie University

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          | DATE:             | June 26 <sup>th</sup> , 20 | 12        |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|-----------|-----------|

| AUTHOR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Khalid Aldubaikhy                                                                                                        | y                 |                            |           |           |

| TITLE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Differential Code-Shifted Reference Impulse-Radio Ultra-Wideband<br>Receiver: Timing Recovery and Digital Implementation |                   |                            |           | and       |

| DEPARTME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ENT OR SCHOOL:                                                                                                           | Department of Ele | ectrical and Co            | mputer En | gineering |

| DEGREE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | M.A.Sc                                                                                                                   | CONVOCATION:      | October                    | YEAR:     | 2012      |

| Permission is herewith granted to Dalhousie University to circulate and to have copied for non-commercial purposes, at its discretion, the above title upon the request of individuals or institutions. I understand that my thesis will be electronically available to the public.  The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.  The author attests that permission has been obtained for the use of any copyrighted material appearing in the thesis (other than the brief excerpts requiring only proper acknowledgement in scholarly writing), and that all such use is clearly acknowledged. |                                                                                                                          |                   |                            |           |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          | Signatur          | re of Author               |           |           |

#### **DEDICATION**

This work is dedicated to my parents, wife, brothers, sisters, and friends for giving me love, support and encouragement.

## إهداء

أهدي هذا العمل المتواضع إلى أبي وأمي وزوجتي وإلى إخوتي وأسرتي جميعاً وإلى جميع أصدقائي الأعزاء على منحي كل الحب و الدعم و التشجيع.

# TABLE OF CONTENTS

| LIST OF TABLES                                         | viii |

|--------------------------------------------------------|------|

| LIST OF FIGURES                                        | ix   |

| ABSTRACT                                               | xiii |

| LIST OF ABBREVIATIONS USED                             | xiv  |

| ACKNOWLEDGEMENTS                                       | XV   |

| CHAPTER 1: INTRODUCTION                                | 1    |

| 1.1 Research Motivation                                | 1    |

| 1.2 Thesis Outline                                     | 2    |

| CHAPTER 2: OVERVIEW OF UWB                             | 4    |

| 2.1 UWB Technology Overview                            | 4    |

| 2.2 UWB DEFINITION AND FCC REGULATIONS                 | 5    |

| 2.3 TYPES OF UWB SIGNALS                               | 8    |

| 2.3.1 Impulse Radio (IR) UWB                           | 9    |

| 2.3.2 Multi-Band OFDM                                  | 9    |

| 2.4 COMPARISON OF UWB WITH EXISTING WIRELESS STANDARDS | 11   |

| 2.5 ADVANTAGES OF IR-UWB TECHNOLOGY                    | 13   |

| 2.6 APPLICATIONS OF UWB.                               | 14   |

| CHAPTER 3: IR-UWB SCHEMES                              | 15   |

| 3.1 Rake Receiver                                      | 15   |

| 3.2 Transmitter Reference (TR)                         | 17   |

| 3.3 Freouency Shifted Reference (FSR)                  | 19   |

| 3.4 CODE SHIFTED REFERENCE (CSR)                                    | 20 |

|---------------------------------------------------------------------|----|

| 3.4.1 The Structure of the CSR-UWB Transmitter                      | 20 |

| 3.4.2 The Structure of the CSR-UWB Receiver                         | 21 |

| 3.4.3 Shifting and Detection Codes Selection for the CSR-UWB System | 23 |

| 3.5 DIFFERENTIAL CODE-SHIFTED REFERENCE (DCSR)                      | 23 |

| 3.5.1 The Structure of the DCSR-UWB Transmitter                     | 24 |

| 3.5.2 The Structure of the DCSR-UWB Receiver                        | 25 |

| 3.5.3 Shifting and Detection Code-Selection for the DCSR-UWB System | 27 |

| 3.5.4 DCSR-UWB Encoding Example                                     | 27 |

| 3.6 Performance Comparison                                          | 29 |

| CHAPTER 4: DCSR IR-UWB SYNCHRONIZATION                              | 32 |

| 4.1 Introduction                                                    | 32 |

| 4.2 Transmitter Structure of the DCSR IR-UWB                        | 34 |

| 4.3 RECEIVER STRUCTURE OF THE DCSR IR-UWB                           | 35 |

| 4.4 SYNCHRONIZATION OF THE DCSR IR-UWB                              | 38 |

| 4.4.1 Timing Recovery Level                                         | 38 |

| 4.4.2 Code Synchronization Level                                    | 52 |

| 4.5 Limitation of the Previous Design of the Timing Recovery        | 57 |

| 4.6 Conclusions                                                     | 59 |

| CHAPTER 5: DCSR IR-UWB TIMING RECOVERY: PROPOSED APPROACH           | 60 |

| 5.1 Introduction                                                    | 60 |

| 5.2 THE PROPOSED TIMING RECOVERY: STRUCTURE AND ALGORITHM           | 61 |

| 5.2.1 The Energy Detector                                           | 63 |

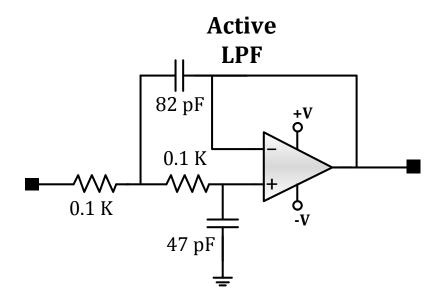

| 5.2.2 The two-pole active LPF                                       | 64 |

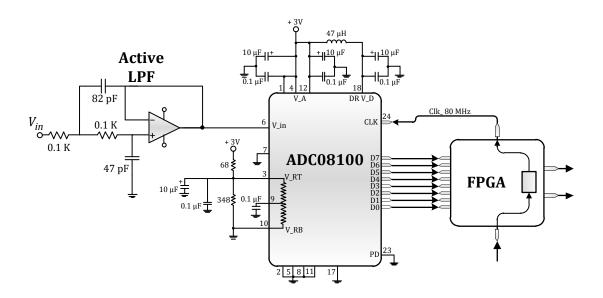

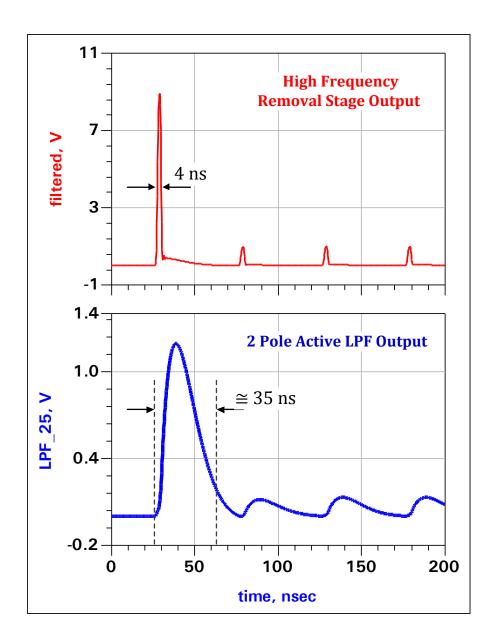

| 5.2.3 The 8-Bit Analog-to-Digital Converter (ADC)                   | 69 |

| 5.2.4 The Timing recovery algorithm                                 |    |

| 5.3 IMPLEMENTATION RESULTS                                          | 81 |

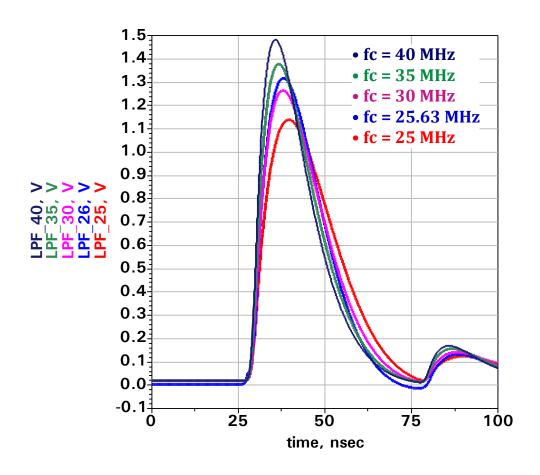

| 5.3.1 The Two-Pole Active LPF                                       | 83 |

| 5.3.2 The PLL Circuit and Timing Recovery Algorithm         | 90  |

|-------------------------------------------------------------|-----|

| 5.4 CONCLUSIONS                                             | 93  |

| CHAPTER 6: CONCLUSIONS                                      | 94  |

| 6.1 Future Work                                             | 95  |

| REFERENCES                                                  | 96  |

| APPENDIX A: THE VHDL CODES OF THE TIMING RECOVERY ALGORITHM | 101 |

| APPENDIX B: THE FULL IMPLEMENTED DCSR IR-UWB SYSTEM         | 106 |

# LIST OF TABLES

| Table 3.1: The selection of the shifting and detection codes example for the CSR-UWB system [1]  | 23 |

|--------------------------------------------------------------------------------------------------|----|

| Table 3.2: The selection of the shifting and detection codes example for the DCSR-UWB system [2] |    |

| Table 3.3: The selection of the shifting and detection codes from Walsh codes when $Nf = 4$ [2]  | 28 |

| Table 3.4: A comparison chart between the TR, FSR, CSR and DCSR systems [26]                     | 31 |

| Table 5.1: The possible situations of the subtraction processes                                  | 76 |

# **LIST OF FIGURES**

| Figure 2.1: FCC definition for the UWB systems                                                                                                                           | .6  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.2: FCC emission spectral mask for indoor UWB communication systems                                                                                              | .7  |

| Figure 2.3: FCC emission spectral mask for outdoor UWB communication systems                                                                                             | .8  |

| Figure 2.4: Gaussian monocycle in the time domain and the frequency domain [5]                                                                                           | .9  |

| Figure 2.5: Channel allocation for MB-OFDM system [10]                                                                                                                   | 0   |

| Figure 2.6: MBOA MB-OFDM Channel allocation [10]                                                                                                                         | 0   |

| Figure 2.7: Different wavelengths of sinusoidal waveforms, which have narrow locations in the spectrum                                                                   | l 1 |

| Figure 2.8: Power levels of UWB signal and a typical narrowband signal1                                                                                                  | 2   |

| Figure 2.9: Multiple users where each one of them can occupy the entire spectrum for a sliver of time [14]                                                               | 12  |

| Figure 2.10: The low-duty-cycle of the UWB pulse where $T_{on}$ represents the time that the pulse exists and $T_{off}$ represents the time that the pulse is absent [5] | 13  |

| Figure 3.1: An example of two MPCs of the Rake receiver structure [17]1                                                                                                  | 5   |

| Figure 3.2: Principle of the (a) Rake receiver and (b) selective Rake receiver [7]1                                                                                      | 6   |

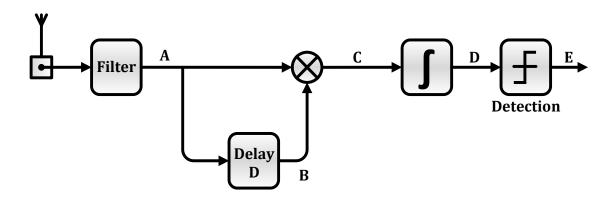

| Figure 3.3: The block diagram of a TR receiver [5]                                                                                                                       | 17  |

| Figure 3.4: Example of TR demodulation where dotted lines represent reference pulses and solid lines represent data pulses [5]                                           | 18  |

| Figure 3.5: FSR-UWB receiver [23]                                                                                                                                        | 9   |

| Figure 3.6: The structure of the CSR-UWB transmitter [1]                                                                                                                 | 21  |

| Figure 3.7: The structure of the CSR-UWB receiver [1]                                                                                                                    | 22  |

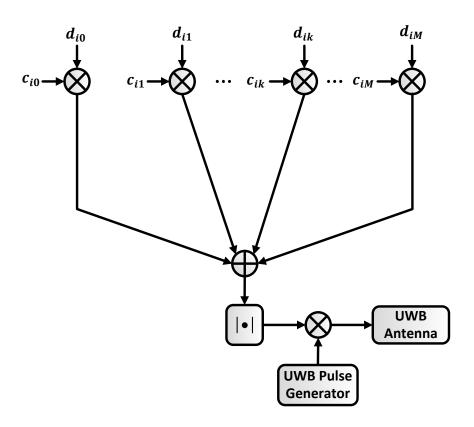

| Figure 3.8: The structure of the DCSR-UWB transmitter [2]                                                                                                                | 24  |

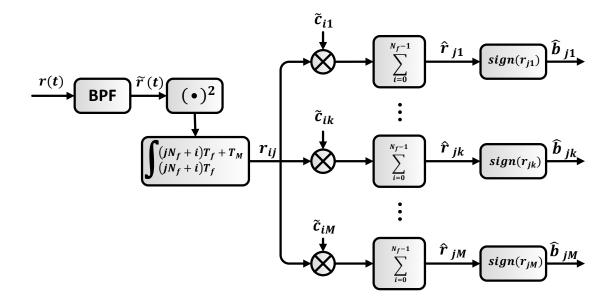

| Figure 3.9: The structure of the DCSR-UWB receiver [2]                                                                          | 25 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

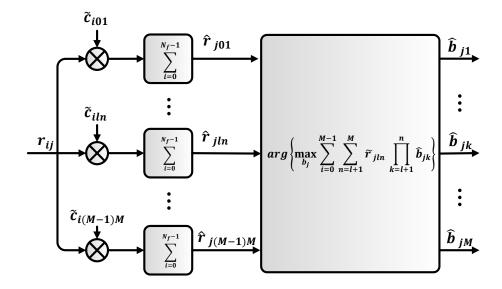

| Figure 3.10: Information bit detection unit of the DCSR-UWB receiver [2]                                                        | 26 |

| Figure 3.11: The amplitudes of the UWB pulses when $b_{J1}=0$ and $b_{J2}=0$                                                    | 29 |

| Figure 3.12: BER comparison between DCSR, CSR, FSR and TR, where M=2 [26]                                                       | 30 |

| Figure 3.13: BER comparison between DCSR, CSR, FSR and TR, where M=3 [26]                                                       | 31 |

| Figure 4.1: The block diagram of the DCSR IR-UWB transmitter [3] [4]                                                            | 34 |

| Figure 4.2: The detailed structure of the DCSR IR-UWB transmitter [3]                                                           | 35 |

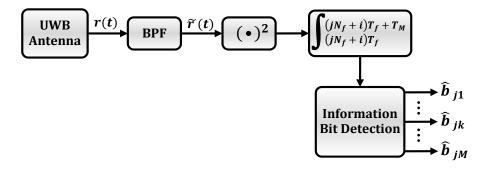

| Figure 4.3: Block diagram of the DCSR IR-UWB receiver [3] [4]                                                                   | 35 |

| Figure 4.4: The detailed structure of the DCSR IR-UWB receiver [3]                                                              | 37 |

| Figure 4.5: The basic block diagram of the PLL circuit                                                                          | 39 |

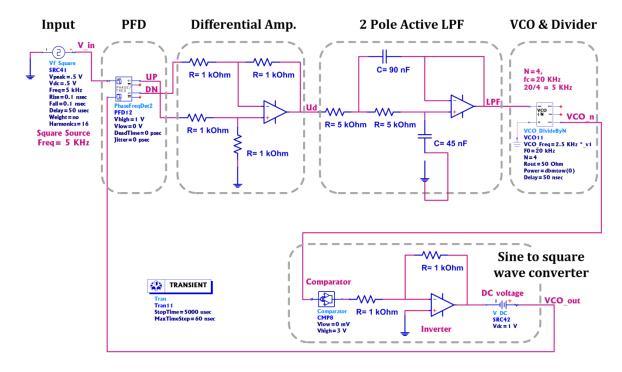

| Figure 4.6: The schematic of the simulated circuit of the PLL circuit                                                           | 41 |

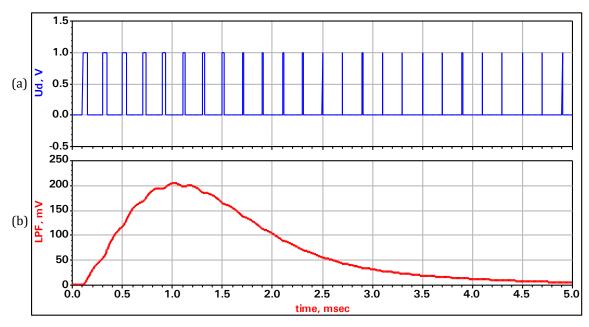

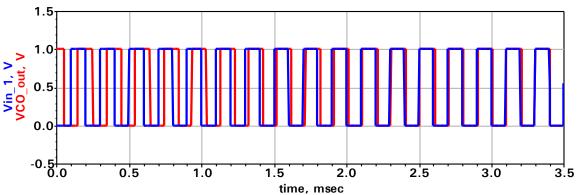

| Figure 4.7: The simulation results of <b>a</b> ) the output of the differential amplifier, and <b>b</b> ) the output of the LPF | 43 |

| Figure 4.8: The simulation result of the PLL loop.                                                                              | 43 |

| Figure 4.9: The synchronization stage of the DCSR IR-UWB receiver                                                               | 44 |

| Figure 4.10: The PLL circuit of the synchronization stage of the DCSR system                                                    | 45 |

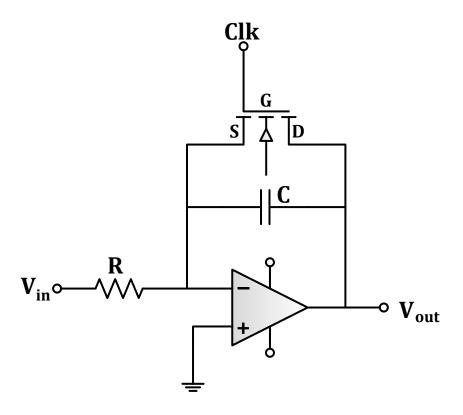

| Figure 4.11: The switch-controlled integrator circuit of the energy detector                                                    | 46 |

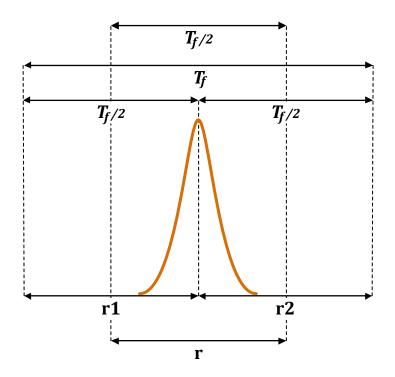

| Figure 4.12: The integration periods of each integrator.                                                                        | 47 |

| Figure 4.13: The previous timing recovery algorithm concept [3] [4]                                                             | 49 |

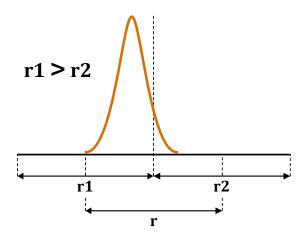

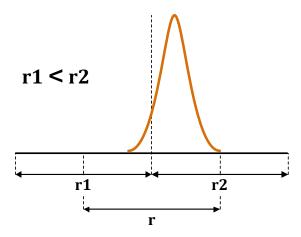

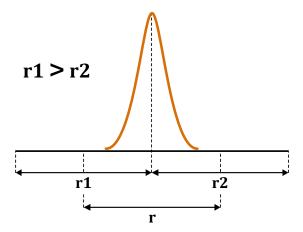

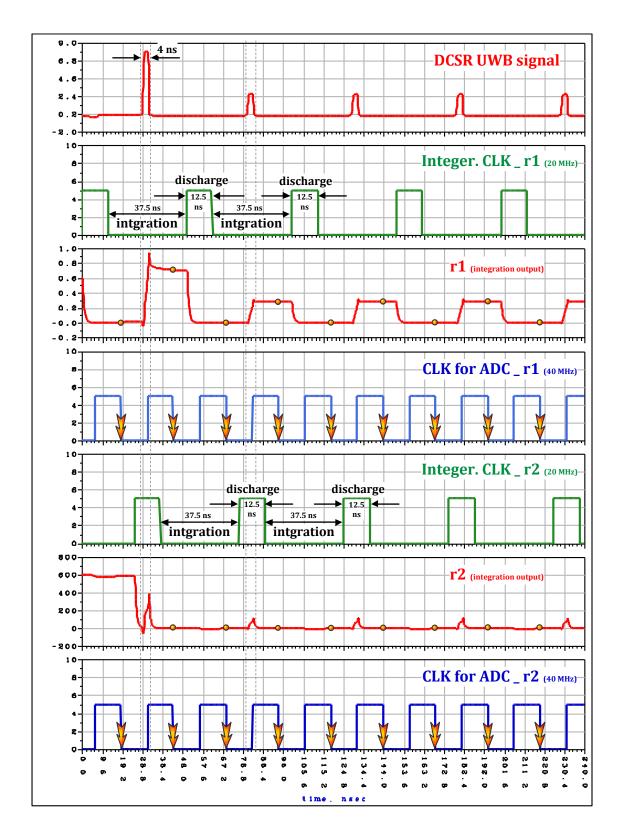

| Figure 4.14: ADS's simulation result when $r_1 > r_2$                                                                           | 50 |

| Figure 4.15: ADS's simulation result when $r_1 < r_2$                                                                           | 51 |

| Figure 4.16: Simulation result of the switch-controlled integrator circuit when $r_1 = r_2$                                     | 52 |

| Figure 4.17: Performance comparison between the three code synchronization algorithms with $M_{avg}$ fixed when $N_f$ =4 and $T_M = T_f$ [40]                                                                                     | 56 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.18: The implementation result of the switch-controlled integrator circuit with a 20 MHz square-wave signal to the input                                                                                                  | 58 |

| Figure 4.19: The implementation result of the switch-controlled integrator circuit with the received DCSR IR-UWB pulses                                                                                                           | 59 |

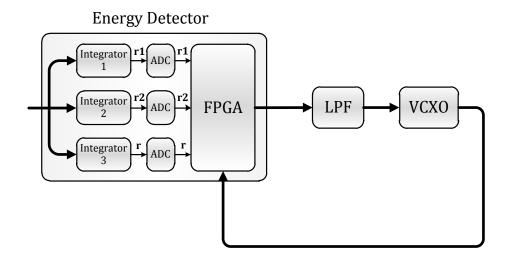

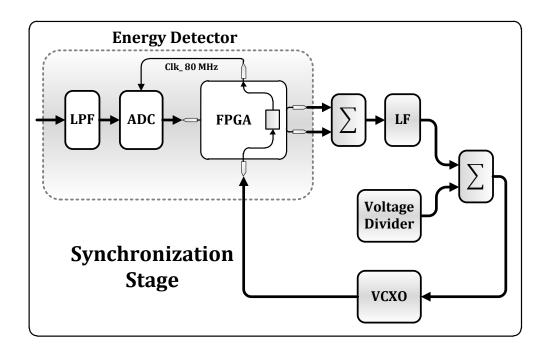

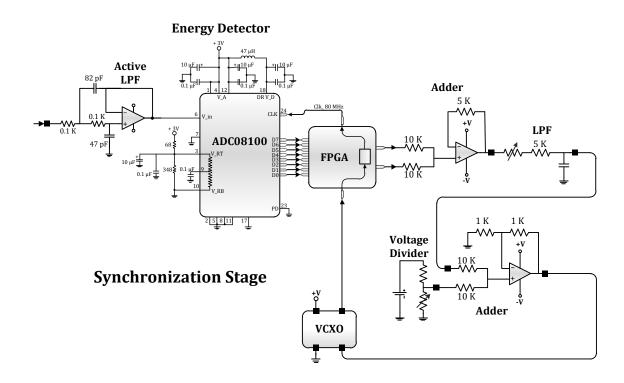

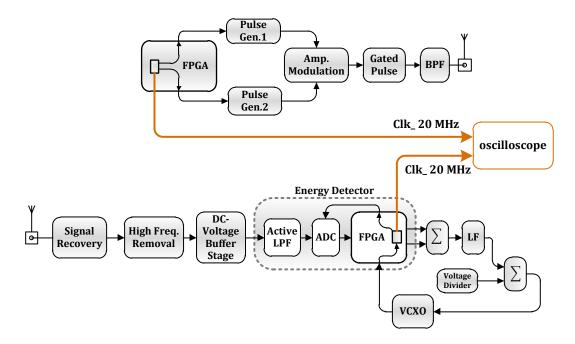

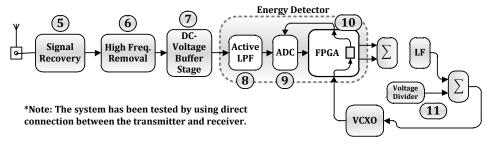

| Figure 5.1: The block diagram of the new synchronization stage of the DCSR IR-UWB receiver                                                                                                                                        | 61 |

| Figure 5.2: The energy detector circuit of the synchronization stage                                                                                                                                                              | 63 |

| Figure 5.3: The two-pole active LPF circuit                                                                                                                                                                                       | 64 |

| Figure 5.4: The simulation results of the two-pole active LPF by using different coefficient values                                                                                                                               | 66 |

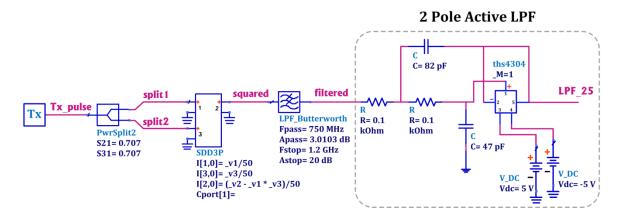

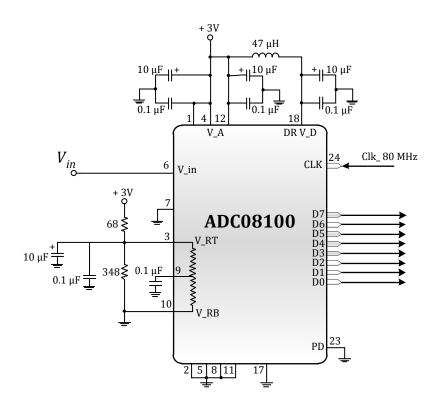

| Figure 5.5: The schematic of the simulated circuit of the two-pole active LPF with the receiver stages of the DCSR IR-UWB system                                                                                                  | 66 |

| Figure 5.6: The simulation results of <b>a</b> ) the received DCSR IR-UWB signal, <b>b</b> ) high frequency removal stage output, and <b>c</b> ) the two-pole active LPF output                                                   | 67 |

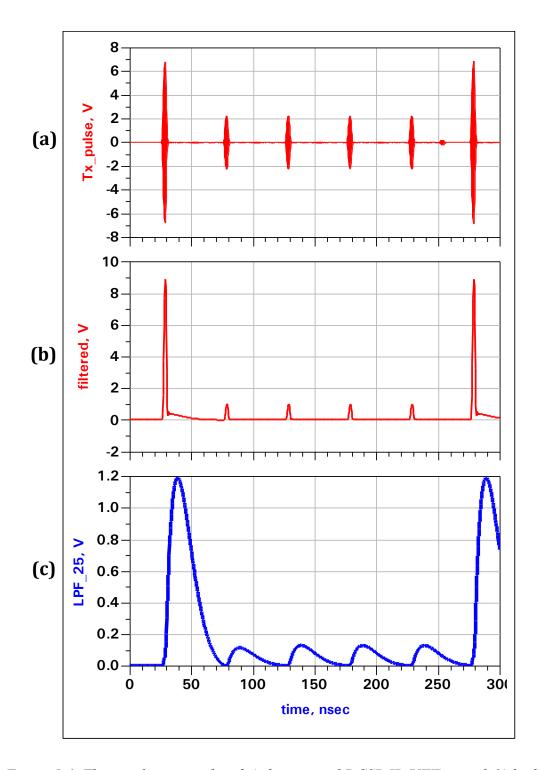

| Figure 5.7: The received DCSR IR-UWB pulses before and after expansion                                                                                                                                                            | 68 |

| Figure 5.8: The reference bias circuit of the 8-Bit A/D Converter (ADC08100)                                                                                                                                                      | 69 |

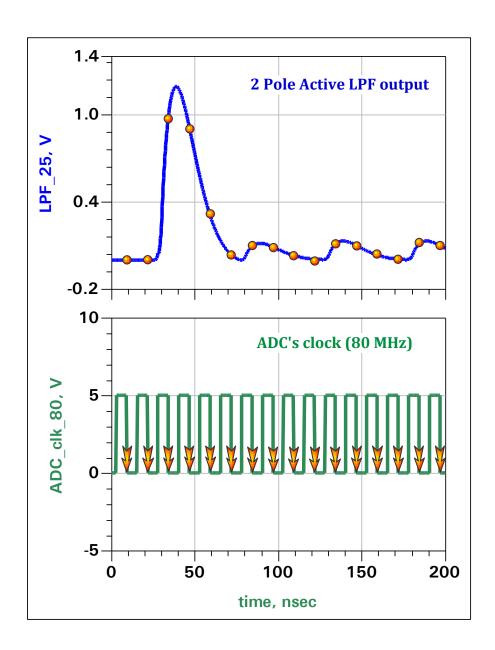

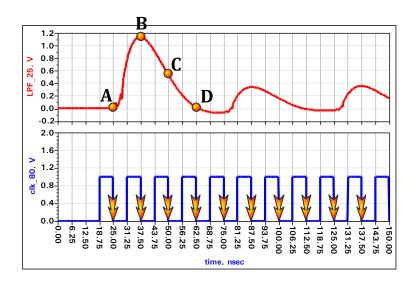

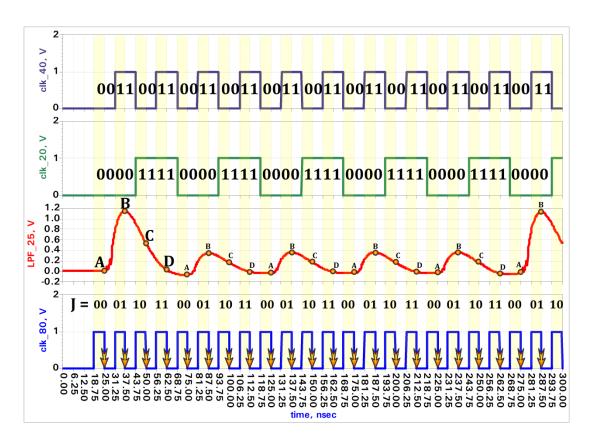

| Figure 5.9: The sample points of the expanded DCSR IR-UWB pulses by using 80 MHz clock                                                                                                                                            | 70 |

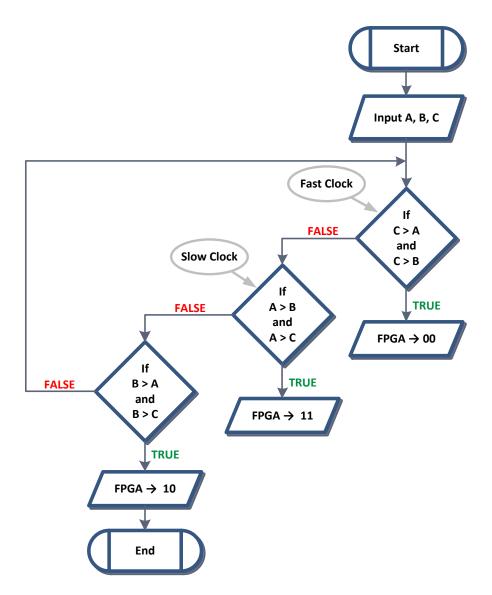

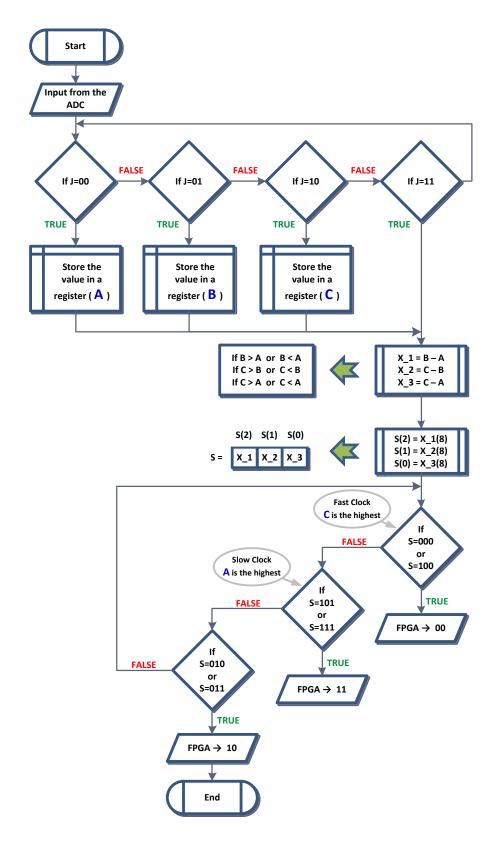

| Figure 5.10: The basic flowchart of the timing recovery algorithm of the DCSR IR-UWB                                                                                                                                              | 71 |

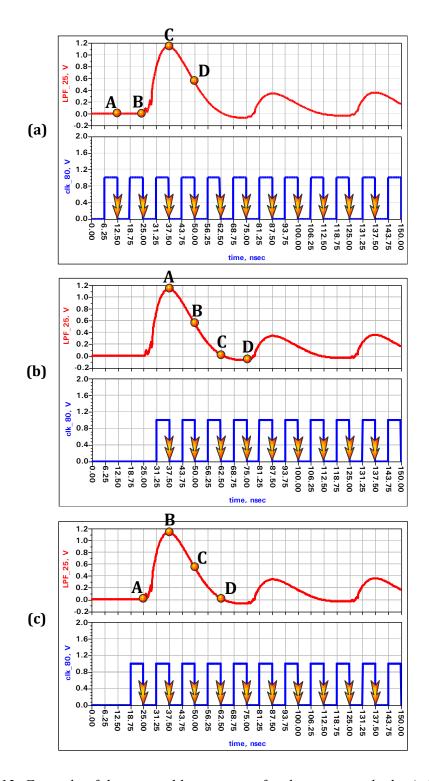

| Figure 5.11: The locations of the four sample points (A, B, C, and D) in the expanded DCSR IR-UWB pulses                                                                                                                          | 72 |

| Figure 5.12: Example of three possible situations for the receiver clock. <b>a)</b> the clock is fast (C is the highest), <b>b)</b> the clock is slow (A is the highest), <b>c)</b> the clock is synchronized (B is the highest). | 74 |

| Figure 5.13: The locations of the sample points                                                                                                                                                                                   | 75 |

| Figure 5.14: The flowchart of the timing recovery algorithm of the DCSR IR-UWB                                                           | 78  |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

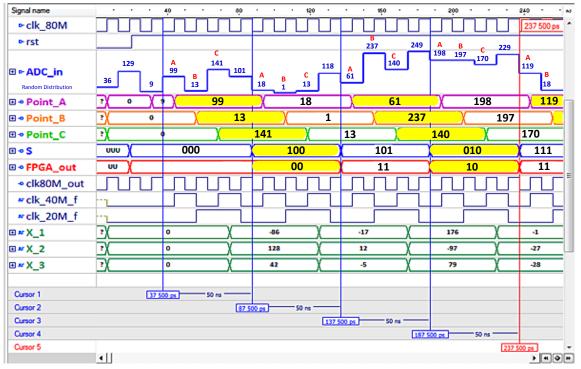

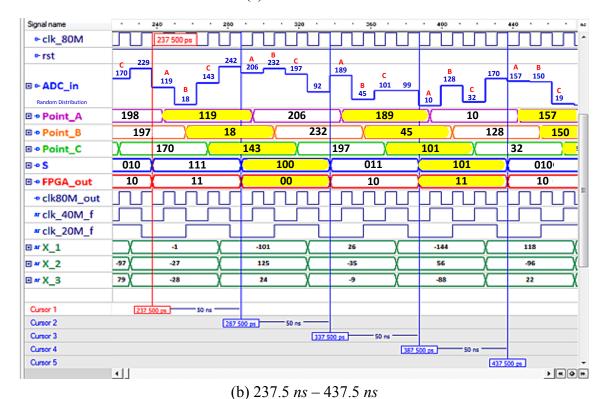

| Figure 5.15: The simulation results of the VHDL codes of the timing recovery algorithm                                                   | 80  |

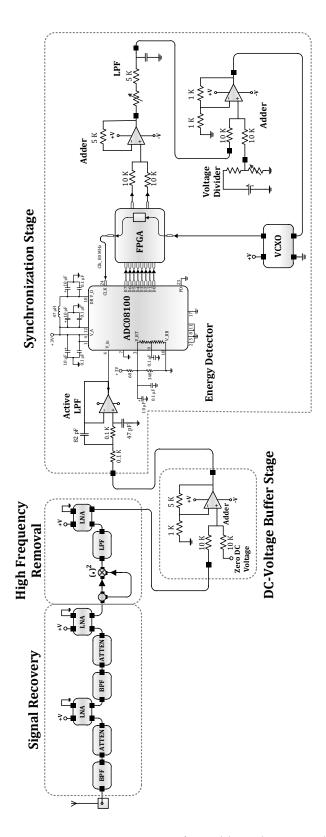

| Figure 5.16: The schematic structure of the new proposed synchronization stage of the DCSR IR-UWB receiver.                              | 81  |

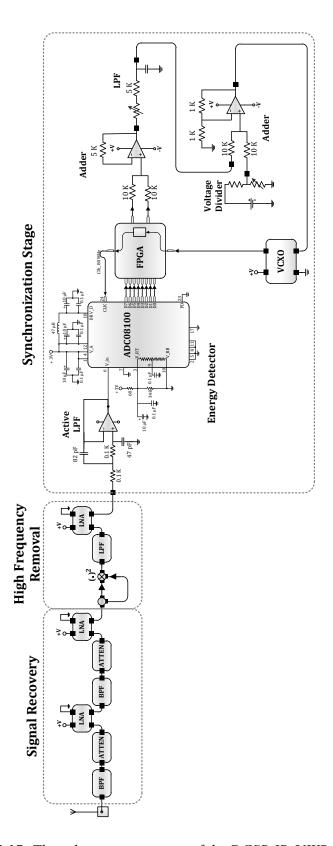

| Figure 5.17: The schematic structure of the DCSR IR-UWB receiver                                                                         | 82  |

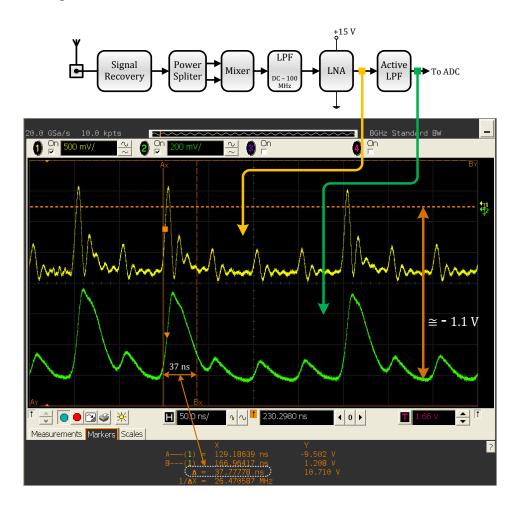

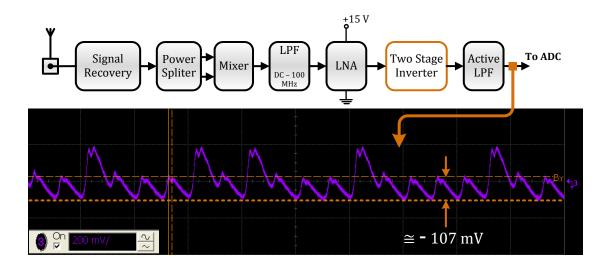

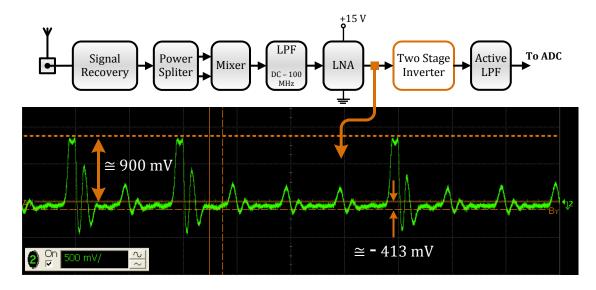

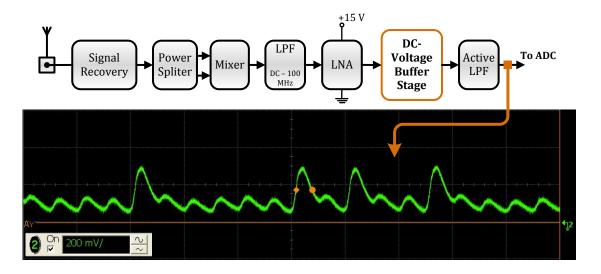

| Figure 5.18: The implementation results before and after the two-pole active LPF circuit                                                 | 84  |

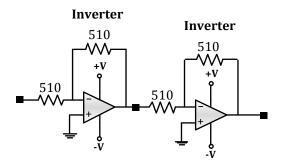

| Figure 5.19: The two stages of the inverter circuit                                                                                      | 85  |

| Figure 5.20: The implementation result of the two-pole active LPF after connecting the two stages of the inverter circuit                | 85  |

| Figure 5.21: The received DCSR IR-UWB signal after the high frequency removal stage                                                      | 86  |

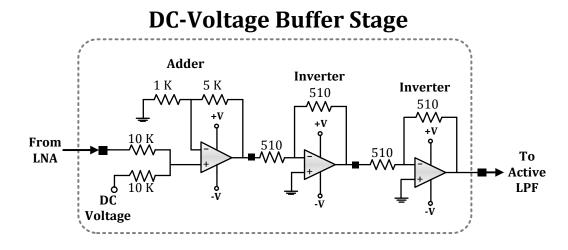

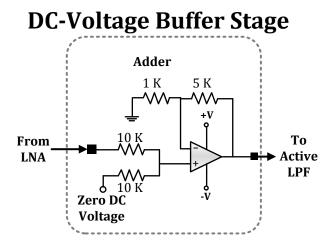

| Figure 5.22: The DC-voltage buffer stage                                                                                                 | 86  |

| Figure 5.23: The output of the two-pole active LPF after connecting the DC-voltage buffer stage.                                         | 87  |

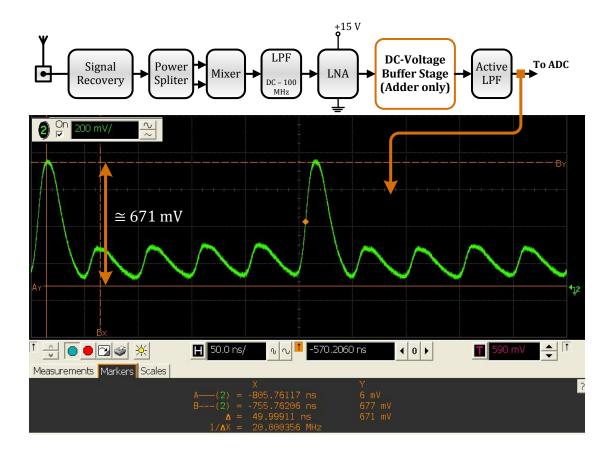

| Figure 5.24: The output of the two-pole active LPF after optimizing the system (using only adder circuit at the DC-voltage buffer stage) | 88  |

| Figure 5.25: The new DC-voltage buffer stage                                                                                             | 88  |

| Figure 5.26: The DCSR IR-UWB receiver after adding the DC-voltage buffer stage                                                           | 89  |

| Figure 5.27: The test scenario of the timing recovery algorithm                                                                          | 90  |

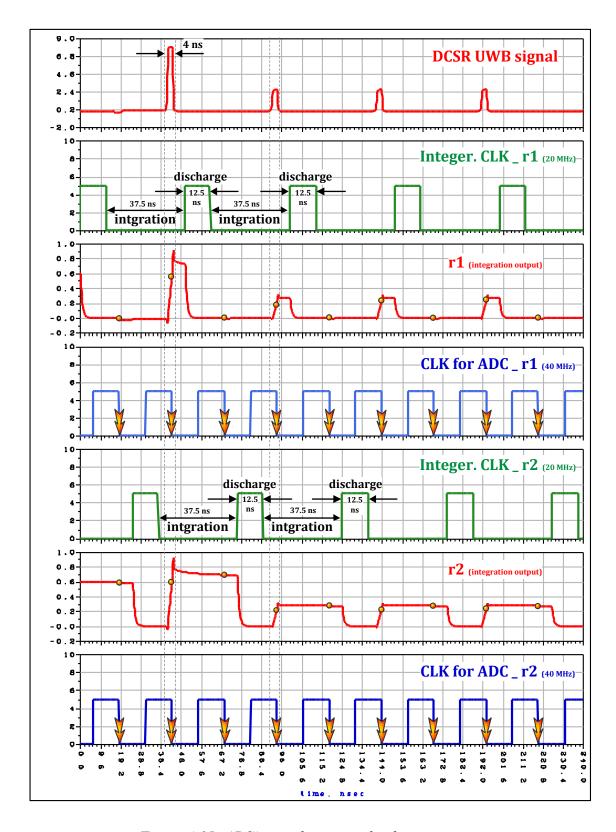

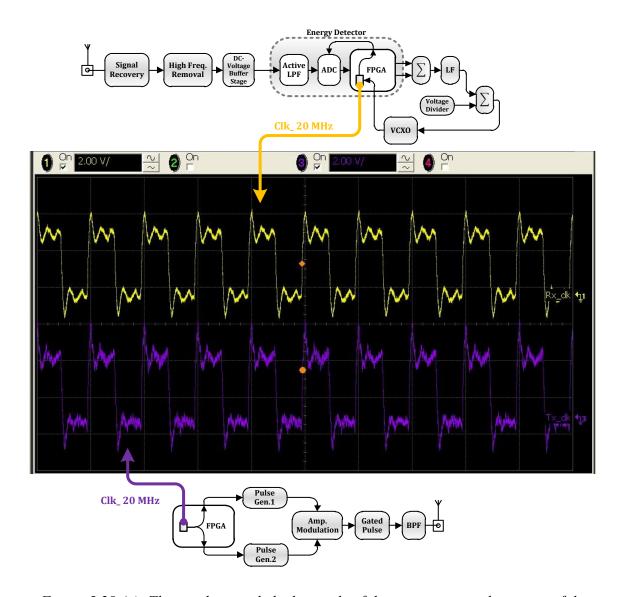

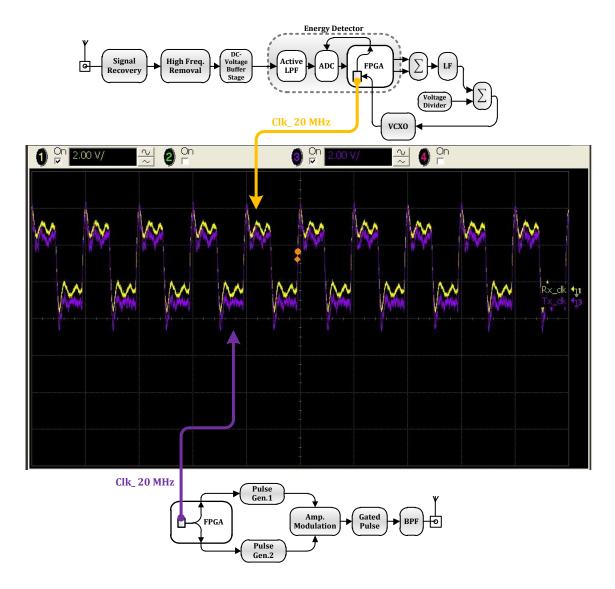

| Figure 5.28 (a): The synchronized clock signals of the transmitter and receiver of the DCSR IR-UWB system                                | 91  |

| Figure 5.28 (b): The synchronized clock signals of the transmitter and receiver of the DCSR IR-UWB system                                | 92  |

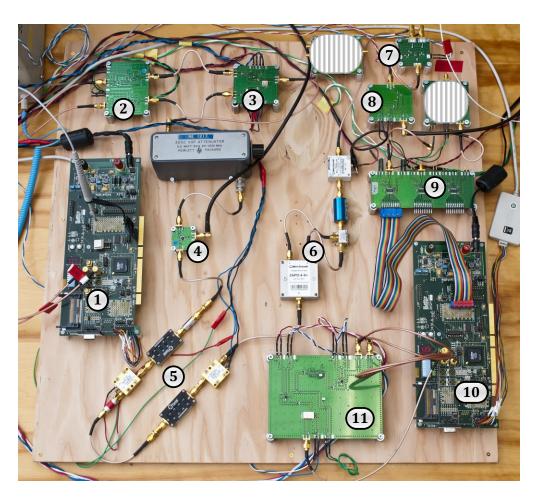

| Figure A.1: Picture of the implemented DCSR IR-UWB system                                                                                | 106 |

#### **ABSTRACT**

Ultra-wideband (UWB) is a wireless system which transmits signals across a much wider frequency spectrum than traditional wireless systems. The impulse radio (IR) UWB technique uses ultra-short duration pulses of nanoseconds or less. The objective of this thesis is to provide the design, implementation and testing of the timing recovery between the transmitter and receiver of the recently emerging differential code-shifted reference (DCSR) Impulse radio (IR) ultra-wideband (UWB) system. A new non-coherent energy detection based technique and its algorithm are proposed for timing recovery by means of a phase-locked loop (PLL) circuit. Simulations are presented first to verify the proposed algorithm. Then, it is implemented and tested in the Lattice ECP2 field-programmable gate array (FPGA) evaluation board with VHDL codes (a VHSIC hardware description language). The simulation and implementation results show that the proposed timing recovery scheme can be effectively achieved without much error.

## LIST OF ABBREVIATIONS USED

A/D Analog to Digital

AC Alternating Current

ADC Analog to Digital Converter

ADS Advanced Design System

ATTEN Attenuator

AWGN Additive White Gaussian Noise

BER Bit-Error Rate

BPF Band-Pass Filter

BW Bandwidth

CSR Code-Shifted Reference

DC Direct Current

DCSR Differential Code-Shifted Reference

DTR Differential Transmitted Reference

FCC Federal Communications Commission

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

FSR Frequency-Shifted Reference

HDL Hardware Description Language

IR Impulse Radio

ISI Inter-Symbol Interference

LF Loop Filter

LNA Low Noise Amplifier

LOS Line-of-Sight

LPF Low-Pass Filter

MB Multi-Band

MPC Multipath Component

NLOS Non-Line-of-Sight

OFDM Orthogonal Frequency Division Multiplexing

PAPR Peak-to-Average Power Ratio

PCB Printed Circuit Board

PD Phase Detector

PFD Phase-Frequency Detector

PLL Phase-Locked Loop

PSD Power Spectral Density

RF Radio Frequency

SMA Subminiature Version A

SNR Signal to Noise Ratio

STER Symbol-Timing-Error Rate

TR Transmitted Reference

UWB Ultra-Wideband

VCO Voltage-Controlled Oscillator

VCXO Voltage-Controlled Crystal Oscillator

VHDL VHSIC Hardware Description Language

#### **ACKNOWLEDGEMENTS**

My unreserved gratitude and praises are for Allah, the Most Compassionate, and the Most Merciful. He blessed me with his bounties, and he has given me the strength and courage to reach my goals during the course of this research.

I would like to express my gratitude to my supervisor, Dr. Zhizhang Chen, for giving me an invaluable opportunity to work on a challenging and interesting project. His guidance and encouragement have inspired and motivated me throughout the completion of this thesis, and he has made my experience worthwhile and enjoyable at the RF/Microwave Wireless Research Laboratory. I would like to extend my gratitude to my co-supervisor, Dr. Hong Nie, for his constant support and encouragement. He has always made himself available for help and advice. I would also like to thank Mr. Blair Macdonald of Cobham Surveillance Ltd. for his valuable discussions and ideas.

I would also like to thank my committee members, Dr. Kamal El-Sankary and Dr. William Phillips, for their willing participation in the process, and for the knowledge gained from them in the classroom and at the lab.

I must also thank Qassim University for selecting me and providing me a Master and Ph.D. scholarship. I truly appreciate the people at Saudi Cultural Bureau in Canada who have been very helpful in the administration of my scholarship.

Thanks to all of my friends and colleagues at the RF/Microwave Wireless Research Laboratory for their support and kindness, and for making my stay memorable. Thanks to Tamim Arabi for working with me on this project, and providing the design and physical structure of the PCB of the proposed timing recovery.

Finally, I would like to thank my parents, Ali Aldubaikhy and Latifah Alfallaj, my brothers and my sisters who have constantly given me love, support and motivation. Last,

but certainly not least, I would like to thank my beloved wife, Haifa Alsuwayyid, for her love, patience and continued encouragement throughout my degree, and also for taking care of our son while I was completing my thesis. Thanks also go to our lovely son, Faris, for showing interest in my thesis at his age of eighteen months. Nothing would have been possible without Allah, the Creator and Lord of the universe, and then my family support.

#### **CHAPTER 1: INTRODUCTION**

This chapter introduces the thesis by providing the research motivations and thesis outline.

#### 1.1 Research Motivation

Although the first wireless transmission was considered to be impulse radio ultra-wideband IR UWB scheme, the dominant scheme for the transmission of wireless communication systems has been the conventional narrowband based on the continuous waveform. The traditional and existing narrowband wireless communication systems suffer from a substantial limitation which is the bandwidth. As the wireless revolution is still developing, ultra-wideband (UWB) technology brings an extraordinary level of attention for its attractive properties, such as the high data-rates in order to overcome the bandwidth limitation. Over the last decade, ultra-wideband technology was only used for military communications, radar, automobile collision, sensing, and positioning systems; however, in February 2002, a fundamental change occurred and it became possible to use UWB for commercial uses with the release of the Federal Communications Commission (FCC) First Report and Order. Subsequently, there has been an increase in research and development for UWB systems.

There are several advantages of the UWB technology which provide a clear comparison between the UWB and conventional narrowband systems. UWB uses ultra-short pulses which occupy an ultra-wide frequency bandwidth; as a result, the data rate of the UWB is increased significantly. UWB systems can work in highly harsh communication environments because of the extremely short pulses. Furthermore, UWB systems have the features of low cost, low radiated power, simple structure, and the advantage of multipath immunity.

The very short pulses and low power of the IR-UWB technology have generated several challenges to the implementation of the IR-UWB systems. In order to recover the transmitted-original information, time synchronization between the transmitter and receiver is one of implementation challenges due to the extremely short pulses of the IR-UWB. The literature shows a number of solutions have been developed over the years in order to address these challenges, such as transmitted reference (TR), and frequency-shifted reference (FSR). Recently, both code-shifted reference (CSR) and differential code-shifted reference (DCSR) have been proposed by our research group to overcome technical challenges and improve the performance of the previous schemes [1] [2].

A transceiver design-structure for the DCSR IR-UWB system including the synchronization system had been implemented by former students in our research group [3] [4]. The synchronization of the impulse radio UWB system involves two steps: Code synchronization and timing recovery. However, it was found that the timing recovery level between the transmitter and receiver was not working as expected due to the requirement of a fast switch in the switch-controlled integrator circuit. Therefore, this thesis aims to provide an alternative scheme for the timing recovery between the transmitter and receiver of the DCSR IR-UWB.

#### 1.2 Thesis Outline

This thesis is organized as follows:

**Chapter 2** provides a general overview of the background of the UWB technology, including UWB definition, types of UWB signaling, IR-UWB advantages and applications of UWB.

The IR-UWB receiver schemes are discussed in **Chapter 3**. The Rake receiver, transmit reference (TR), frequency-shifted reference (FSR), code-shifted reference (CSR), and differential code-shifted reference (DCSR) systems are examined according to their

structure and improvement. A performance comparison between the TR, FSR, CSR, and DCSR systems is provided.

The history of UWB synchronization and the implementation of the DCSR IR-UWB synchronization are outlined in **Chapter 4**. The implementation transceiver structure design of the DCSR IR-UWB is explained briefly in this chapter. Both the previous timing recovery scheme by means of a phase-locked loop (PLL) circuit and the code synchronization level of the DCSR IR-UWB system are analyzed and discussed. The results obtained after implementation of the switch-controlled integrator circuit at the previous timing recovery level is provided and compared to the simulation results.

Chapter 5 provides the proposed non-coherent timing recovery of the DCSR IR-UWB receiver and its algorithm. This timing recovery is based on the energy detection technique by means of a phase-locked loop (PLL) circuit. The design of the energy detector and the field programmable gate array (FPGA) with VHDL codes (a VHSIC hardware description language) are explained. Both the simulation and implementation results are presented.

**Chapter 6** gives a conclusion of the research efforts of this thesis. Future work is recommended and discussed.

**Appendix** includes the VHDL codes to program the FPGA for the proposed timing recovery algorithm of the DCSR IR-UWB receiver and a picture of the full implemented DCSR IR-UWB system

## **CHAPTER 2: OVERVIEW OF UWB**

Ultra-wideband (UWB) is a wireless system that transmits signals by using a large part of radio frequency (RF) spectrum by using very low energy. Originally, UWB signal was the pure, first, wireless transmission approach which was transmitted by the Marconi spark gap transmitter. The Federal Communications Commission (FCC) received several demands during the past decade for approving the operation of the unlicensed UWB system to coexist with the existing communication systems. Consequently, the FCC authorizes the unlicensed UWB system to operate in several ranges of frequencies on February 14, 2002.

Single band and multi-band are the two types of UWB signals. The single band is known as the impulse radio (IR), which was introduced as the spark gap transmission system. Multi-band orthogonal frequency division multiplexing (MB-OFDM) is the second type of UWB signaling.

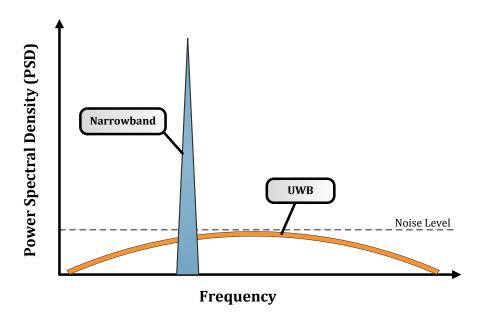

UWB technology is different from narrowband systems in many features such as, the portion allocation of radio frequency (RF) and the power spectral density (PSD) level. The channel capacity of the UWB is increased and the complexity of the transceiver structure is decreased due to the wide bandwidth and the radio frequency of the UWB technology. UWB generates considerable interest and promise for different types of applications because the UWB technology combines the high data rate and the large range of bandwidth.

#### 2.1 UWB Technology Overview

UWB is not new technology, it has been known for a long time as a spark gap radio transmission system. At one time, there was no consideration to the advantage of the

bandwidth provided by the short pulses. The first time that UWB technology was used was when Gugliemo Marconi used the spark gap radio transmitter to convey Morse code sequences across the Atlantic Ocean in 1901 [5]. Although sinusoidal waves are the technique for the existing wireless communication system, the first wireless communication systems were impulse radio scheme. Impulse radio wireless communication was introduced as the spark gap transmission system. Subsequently, sinusoidal wireless communication became the main technique of wireless communication systems until the 1960s [6].

Military communications, radar, automobile collision, sensing, and positioning systems are the applications that have been used by the UWB technology for the last 20 years [6]. UWB applications were developed in the military and United States Government projects; however, there were plans to find commercial uses for the UWB systems in the late 1990s [7]. In 2002, a significant change occurred with release of the Federal Communications Commission (FCC) First Report and Order [4], making it possible to use UWB for commercial uses.

#### 2.2 UWB Definition and FCC Regulations

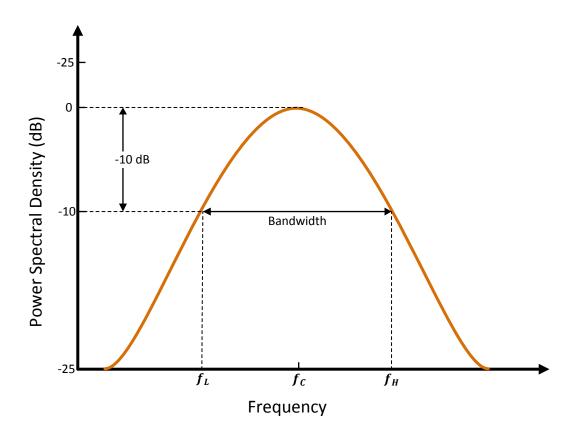

According to the FCC, ultra-wideband (UWB) is a system with a radio signal that occupies a bandwidth of more than 500 MHz or a fractional bandwidth ( $B_f$ ) greater than 20% [8]. Figure 2.1 represents the FCC UWB definition, and the mathematical expression of this definition can be expressed as:

$$BW = (f_H - f_L) \ge 500 \text{ MHz}$$

(2.1)

or,

$$B_f = \frac{BW}{f_c} = \frac{f_H - f_L}{(f_H + f_L)/2} \ge 20\%$$

(2.2)

Where,  $f_H$  is the upper frequency of the -10 dB emission point,  $f_L$  is lower frequency of the -10 dB emission point, and  $f_c$  is the center frequency and is expressed as:

$$f_c = \frac{f_H - f_L}{2} \tag{2.3}$$

Figure 2.1: FCC definition for the UWB systems

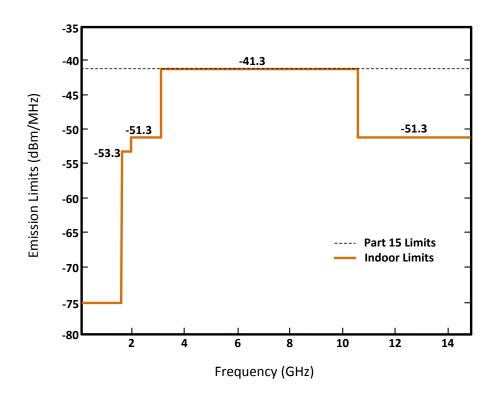

The large spectrum of UWB technology results in the UWB systems interference with existing wireless communication systems. As a result, in 2002 the FCC set rules and recommendations for UWB wireless devices to work under particular power spectral masks. According to the United States Federal Communications Commission (FCC), the spectral mask for UWB communication systems is between 3.1 GHz and 10.6 GHz for commercial devices. In addition, the FCC specifies the maximum power spectral density

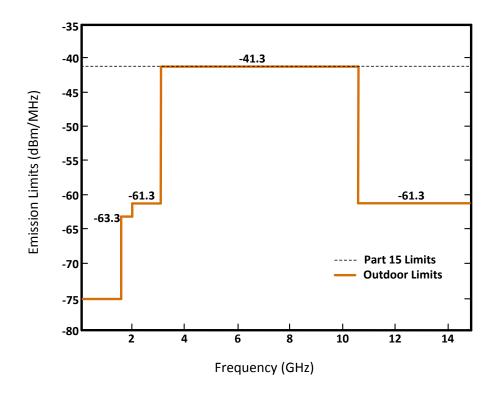

at -41.3 dBm/MHz and the minimum bandwidth (BW) at 500 MHz or 20% of the center frequency. The indoor FCC emission spectral mask for UWB communication systems is shown in Figure 2.2. However, the FCC has allocated a different spectral mask for outdoor UWB communication systems which are lower than indoor UWB communication systems by 10 dBm/MHz as it is shown in Figure 2.3 [8].

Figure 2.2: FCC emission spectral mask for indoor UWB communication systems

Figure 2.3: FCC emission spectral mask for outdoor UWB communication systems

### 2.3 Types of UWB Signals

Impulse radio (IR) and multi-band orthogonal frequency division multiplexing (MB-OFDM) are the two common UWB signalling types. The impulse radio (IR) technology generates ultra-short pulses to achieve an extremely wide bandwidth in the spectrum [9]. However, in the multi-band UWB system, the whole 7.5 GHz UWB spectrum is divided into several sub bands with 500 MHz wide or greater [9] [10] [11]. The type of UWB transmission that is used in this thesis is the IR-UWB. In the following subsections, each approach of UWB signalling will be explained briefly.

#### 2.3.1 Impulse Radio (IR) UWB

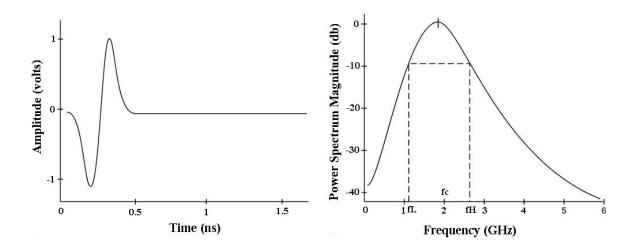

In this approach, the transmission of ultra-short pulses or pulsed waveforms is producing the IR UWB signals for low data rate applications. As discussed in Section 2.2, the FCC defined the UWB signals that the bandwidth is greater than 500 MHz or the fractional bandwidth is greater than 0.25. Therefore, there are several pulse shapes such as Gaussian that suite with the FCC's definition. Figure 2.4 shows the Gaussian monocycle. In the IR UWB, as there is no need for a carrier modulation which is a baseband technique, the system has the advantage of low complexity transceiver. Furthermore, the system can be designed with low power consumption because of the low duty cycle of the remarkably short UWB pulse [9].

Figure 2.4: Gaussian monocycle in the time domain and the frequency domain [5]

#### 2.3.2 Multi-Band OFDM

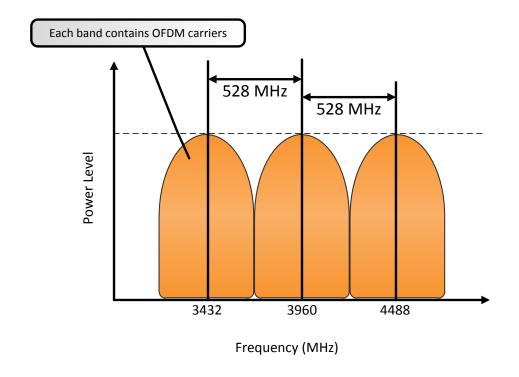

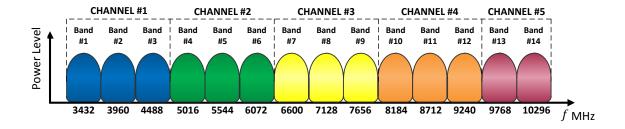

Multi-band orthogonal frequency division multiplexing (MB-OFDM) UWB approach splits the UWB band into several frequency bands where each band is equal to or larger than 500 MHz; therefore, the FCC requirements for the minimum bandwidth are applied [9] [10]. Figure 2.5 shows the MBOA (multiband OFDM Alliance) proposal of the channel allocation for the first band group for the MB-OFDM where the data is

transmitted over multiple subcarriers with 528 MHz channel wide. The whole UWB spectrum (7.5 GHz) can be divided into 14 sub bands and they are grouped into five channels as shown in Figure 2.6. For standard operation, the first three of the 14 sub bands are mandatory for UWB transmission; however, the other sub bands are considered optional [11] [10] [12].

Figure 2.5: Channel allocation for MB-OFDM system [10]

Figure 2.6: MBOA MB-OFDM Channel allocation [10]

The complexity and the power consumption of the MB-OFDM will increase when the data rate increases [13]. Advanced analog-to-digital converters (ADC), Viterbi decoders, and Fast Fourier Transform (FFT) engines are examples of complex components that are needed in the MB-OFDM UWB system [13]. Although this approach increases the complexity of the system, the synchronization is easier, and the inter-symbol interference (ISI) can be avoided because of the longer symbol period duration for the individual sub bands in the OFDM [11].

#### 2.4 Comparison of UWB with Existing Wireless Standards

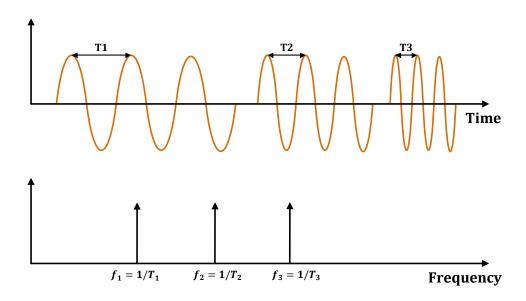

Traditional communication systems use sinusoidal continuous waveforms which have narrowband locations in the spectrum as shown in Figure 2.7. However, UWB technology uses ultra-short signals which have large spectrum (ultra wide bandwidth), and they can be modulated in time rather than frequency [5] [7] [14]. The difference between the narrowband and UWB communication system is shown in Figure 2.8 [5] [7] [14].

Figure 2.7: Different wavelengths of sinusoidal waveforms, which have narrow locations in the spectrum

Figure 2.8: Power levels of UWB signal and a typical narrowband signal

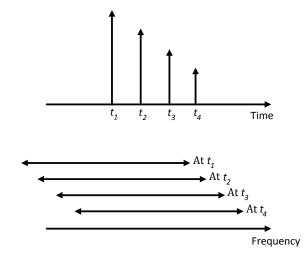

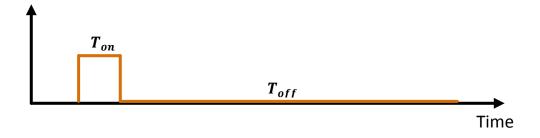

As information signals are separated in time in UWB, each user can have large bandwidth, as shown in Figure 2.9. In addition, since UWB uses ultra-short impulse signals (in the range of nanoseconds), UWB devices consume much lower power because of the low duty cycle of the information as it is shown in Figure 2.10 [5] [7] [14].

Figure 2.9: Multiple users where each one of them can occupy the entire spectrum for a sliver of time [14]

Figure 2.10: The low-duty-cycle of the UWB pulse where  $T_{on}$  represents the time that the pulse exists and  $T_{off}$  represents the time that the pulse is absent [5]

#### 2.5 Advantages of IR-UWB technology

There are various unique advantages of IR-UWB systems. The IR-UWB technology has the following four main advantages [5] [6]:

1. The channel capacity or data rate of the UWB is increased significantly due to the large bandwidth that is produced from UWB pulses. From Shannon's communication theory [15]:

$$C = BW \log_2(1 + SNR) \tag{2.4}$$

Where, C is the channel capacity, BW is the bandwidth, and SNR is the signal-to-noise ratio. The channel capacity C increases with bandwidth BW linearly; therefore, the data rate will increase because of the extremely large bandwidth of the UWB.

2. UWB can work with low *SNR*, and it can work with harsh communication channels. From Equation (2.4): the channel capacity *C* decreases with *SNR* logarithmically; however, the channel capacity is still extremely large due to the large bandwidth of UWB communication systems.

- 3. Another advantage of UWB is the low equipment cost as UWB modulates the pulse directly without the need of a carrier as narrowband and wideband systems. Hence, UWB has a simple transceiver architecture.

- 4. UWB has the advantage of multipath immunity because of the short duration of UWB pulses (with nanosecond range). For this reason, there is a low probability for a reflected pulse to collide with the line-of-sight (LOS) pulse.

#### 2.6 Applications of UWB

UWB applications were limited to military communications and radar. However, after the FCC allocated spectrum for UWB systems in the FCC First Report and Order on February 14, 2002, several new applications have been developed and suggestions made for improvement of existing products. For instance, new applications for the wireless industry, as well as integrating existing wireless system, is considered as one of the advantages of the UWB technology [5] [8].

Communications, distance determinations, remotely sensing radar, and vehicular radar are the main categories of the UWB applications [8].

Therefore, since the UWB combines the high data rate and the large range of bandwidth, UWB generates keen interest and promise for different types of applications.

### **CHAPTER 3: IR-UWB SCHEMES**

The challenge of the receiver design has been a serious obstacle to the implementation of UWB technology. The literature shows a number of studies which have developed different solutions to address this issue.

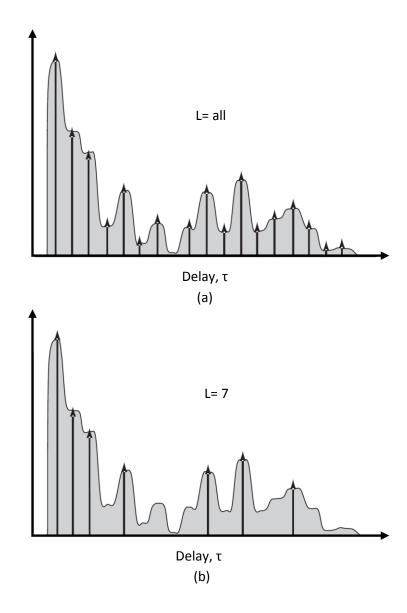

#### 3.1 Rake Receiver

Whereas the UWB channel is abundantly rich in multipath components (MPCs), especially for the non-line-of-sight (NLOS) environments, a diversity technique can be employed, such as the Rake receiver, to improve the received signal energy [7] [16]. Figure 3.1 shows an example of two MPCs of the general structure of the Rake receiver in which a detecting figure is required in each resolvable MPCs. In addition, in order to match the amplitude, phase, and delay of each MPCs, channel estimation, multipath acquisition, and tracking operations are required for each detecting finger. The received signal energy and the multipath components of the signal can be combined by the Rake receiver [7].

Figure 3.1: An example of two MPCs of the Rake receiver structure [17]

However, because of the large number of the detecting fingers in the UWB channel which is much higher than any other wireless system, the implementation of the Rake receiver becomes complex [1] [18].

Although the selective Rake receiver was proposed to improve the complexity and the performance of the Rake receiver by assigning limited detecting fingers, the complexity and cost is still needed [7] [9] [19]. A comparison of the principle of the Rake receiver and selective Rake receiver is shown in Figure 3.2.

Figure 3.2: Principle of the (a) Rake receiver and (b) selective Rake receiver [7]

#### 3.2 Transmitter Reference (TR)

The transmitted reference receiver was then introduced for its simplicity and to avoid the need of the pulse-detection technique. The TR scheme transmits the first pulse which is an un-modulated reference pulse followed by a data modulated pulse after a known time delay (D). Figure 3.3 shows the block diagram of a TR receiver. In order to recover the transmitted information, the received IR UWB signals and the delayed version of the signals are correlated with each other in the TR receiver as shown in Figure 3.4. These two pulses experience the same channel distortion and multipath fading [5] [20] [21].

Figure 3.3: The block diagram of a TR receiver [5]

Even though the TR scheme reduces the complexity of the receiver, the performance of the TR is limited due to the requirement of delay element which is difficult to implement in the integrated circuit [22] [23]. In addition, because of the overlap between the reference and data pulse, a correlation of noise on noise appears and decreases the performance of the TR [20].

Figure 3.4: Example of TR demodulation where dotted lines represent reference pulses and solid lines represent data pulses [5]

#### 3.3 Frequency Shifted Reference (FSR)

Subsequently, a slightly frequency shifted reference FSR UWB scheme was proposed to deal with the issue of TR UWB. The FSR UWB scheme separates the reference signal and data signal in the frequency domain rather than in the time domain; as a result, the delay element is not required at the FSR UWB receiver [23] [24].

The FSR sends out a reference pulse sequence and multiple pulse sequence at the same time; however, a defined frequency tone slightly shifts each data pulse sequence. In addition, for the FSR system the reference and data sequence pulses experience the same distortion channel; therefore, the frequency offset between them needs to be smaller than the channel coherent bandwidth [23] [24].

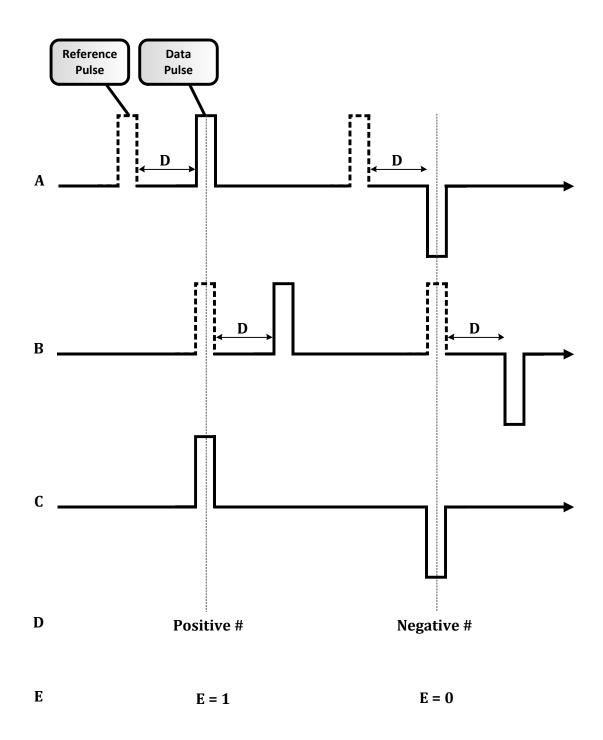

Figure 3.5 shows the structure of the FSR UWB receiver. In this figure, the FSR UWB uses only one data sequence which has the same frequency offset used in the transmission. In order to extract information from the data pulse sequences, the frequency offset is going to shift the reference pulse sequences in the receiver.

Figure 3.5: FSR-UWB receiver [23]

However, the implementation of the FSR UWB approach is complex because of the analog carrier operation. Furthermore, the performance is limited due to frequency, phase, and amplitude errors caused by oscillator mismatch, multipath fading, and nonlinear amplifiers respectively [1].

# 3.4 Code Shifted Reference (CSR)

Recently, a code-shifted reference ultra-wideband (CSR-UWB) has been introduced for the IR-UWB receiver. While the reference and data pulse sequence are separated in time domain in the TR-UWB system and in frequency domain in the FSR-UWB system, the reference and data pulse sequences are separated by codes in the CSR-UWB scheme [1]. As a result, the performance of the system is increased because the CSR-UWB system does not require a delay element or a frequency conversion.

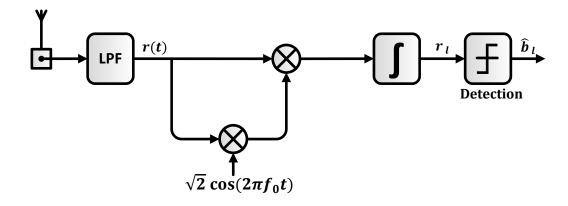

#### 3.4.1 The Structure of the CSR-UWB Transmitter

A reference pulse sequence and one or more data pulse sequences are transmitted at the same time in the CSR-UWB transmitter. The structure of the CSR-UWB transmitter is shown in Figure 3.6, and the expression of the transmitted CSR-UWB signal is [1]:

$$x(t) = \sum_{j=-\infty}^{\infty} \sum_{i=0}^{N_f - 1} P[t - (jN_f + i)T_f] \left| \sqrt{M} c_{io} + \sum_{k=1}^{M} b_{jk} c_{ik} \right|$$

(3.1)

Where, p(t) is the  $T_P$  duration UWB pulse,  $T_f$  is the time between the pulses,  $N_f$  is the number of frames transmitted,  $b_{jk} \in \{-1,1\}$  is the  $k^{th}$  information bit which transmitted during the  $j^{th}$   $N_f$   $T_f$  time duration,  $c_{ik} \in \{-1,1\}$  is the (M+1) shifting codes, and M is the number of information bits [1].

Figure 3.6: The structure of the CSR-UWB transmitter [1]

The CSR-UWB transmits M information bits for every  $N_f$  frames, where  $M \le 2^{N-1}$  and  $N_f = 2^N$ . In addition, the information bits (M) are set by the shifting codes (M+1) at the transmitter to separate the reference pulse sequence from the data pulse sequence orthogonally [1]. The (M+1) shifting codes is [1]:

$$\begin{bmatrix}

c_0 \\

\vdots \\

c_k \\

\vdots \\

c_M

\end{bmatrix} = \begin{bmatrix}

c_{00} & \cdots & c_{i0} & \cdots & c_{(N_f-1)0} \\

\vdots & \vdots & \vdots & \vdots & \vdots \\

c_{0k} & \cdots & c_{ik} & \cdots & c_{(N_f-1)k} \\

\vdots & \vdots & \vdots & \vdots & \vdots \\

c_{0M} & \cdots & c_{iM} & \cdots & c_{(N_f-1)M}

\end{bmatrix}$$

(3.2)

#### 3.4.2 The Structure of the CSR-UWB Receiver

As shown in Figure 3.7, the received signal of the CSR-UWB system passes through the following [1]. First, In order to eliminate the noise and interference, the received signal is passed through a band-pass filter (BPF). Then, a square unit is applied to the filtered signal. In order to obtain  $r_{ij}$ , the squared signal is then integrated from  $(jN_f + i)T_f$  to  $(jN_f + i)T_f + T_M$ , where  $T_M$  is varied from  $T_P$  to  $T_f$  in an additive white Gaussian noise

(AWGN) channel and in a multipath channel respectively. Finally, the signal  $(r_{ij})$  is decoded by the M detection codes at the receiver to get the original information bits [1].

Figure 3.7: The structure of the CSR-UWB receiver [1]

The *M* detection codes can be expressed as Equation (3.3):

$$\begin{bmatrix} \tilde{\boldsymbol{c}}_{\boldsymbol{0}} \\ \vdots \\ \tilde{\boldsymbol{c}}_{\boldsymbol{k}} \\ \vdots \\ \tilde{\boldsymbol{c}}_{\boldsymbol{M}} \end{bmatrix} = \begin{bmatrix} \tilde{c}_{00} & \cdots & \tilde{c}_{i0} & \cdots & \tilde{c}_{(N_f-1)0} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ \tilde{c}_{0k} & \cdots & \tilde{c}_{ik} & \cdots & \tilde{c}_{(N_f-1)k} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ \tilde{c}_{0M} & \cdots & \tilde{c}_{iM} & \cdots & \tilde{c}_{(N_f-1)M} \end{bmatrix}$$

(3.3)

The logic '1' or '0' is determined by the sign of the correlation results of the signal  $(r_{ij})$  and M detection codes after adding them independently [1].

# 3.4.3 Shifting and Detection Codes Selection for the CSR-UWB System

The shifting codes and detection codes have been selected from Walsh codes for the sake of detecting the transmitted information bits accurately in the receiver side of the CSR-UWB scheme [1]. An example of the selection of the shifting codes and detection codes for the CSR-UWB system is given in Table 3.1.

Table 3.1: The selection of the shifting and detection codes example for the CSR-UWB system [1]

| Code<br>Length | Shifting Codes                                            | Detection Codes                                                                                                                                                                                             |  |

|----------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $N_f = 2$      | $c_0 = [1, 1]$ $c_1 = [1, -1]$                            | $\widetilde{c}_1 = [1, -1]$                                                                                                                                                                                 |  |

| $N_f = 4$      | $c_0 = [1,1,1,1]$ $c_1 = [1,-1,1,-1]$ $c_2 = [1,1,-1,-1]$ | $\widetilde{c}_{1} = [1, -1, 1, -1]$ $\widetilde{c}_{2} = [1, 1, -1, -1]$                                                                                                                                   |  |

| $N_f = 8$      | $c_0 = [ \ 1 \ ,1 \ ,1 \ ,1 \ ,1 \ ,1 \ ,1 \ ,$           | $\widetilde{c}_{1} = [1, -1, 1, -1, 1, -1, 1, -1]$ $\widetilde{c}_{2} = [1, 1, -1, -1, 1, 1, -1, -1]$ $\widetilde{c}_{3} = [1, 1, 1, 1, -1, -1, -1, -1]$ $\widetilde{c}_{4} = [1, -1, -1, 1, -1, 1, 1, -1]$ |  |

# 3.5 Differential Code-Shifted Reference (DCSR)

Although the CSR-UWB scheme was proposed to avoid the requirement of the delay element or the frequency conversion, the CSR-UWB system spends power to transmit the reference pulse sequence. As a result, the bit-error rate performance of the CSR-UWB scheme is like the TR system since the TR scheme spends half of its power transmitting the reference pulse [25]. In order to reduce the power that is used to transmit the reference

pulse sequence, and also to improve the bit-error rate (BER) performance, a differentially code-shifted reference has been introduced by simultaneously transmitting the differentially encoded information bits (M). Consequently, the transmitting power is reduced from half to 1/(M+1) since one data pulse sequence can be used as a reference for another pulse sequence [2].

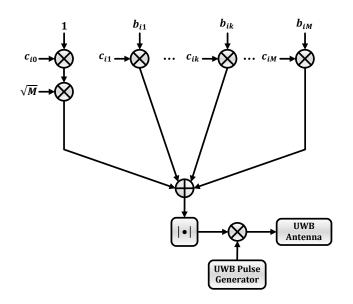

#### 3.5.1 The Structure of the DCSR-UWB Transmitter

The general structure of the DCSR-UWB transmitter is shown in Figure 3.8. The DCSR transmitter is the same as the CSR transmitter except the information bits  $(b_{jk})$  are differentially encoded first  $(d_{jk})$ . The DCSR-UWB scheme transmits  $M(M+1)/2 \le 2^N - 1$  of information bits per  $N_f = 2^N$  frame [2].

Figure 3.8: The structure of the DCSR-UWB transmitter [2]

The mathematical expression of the proposed scheme is [2]:

$$x(t) = \sum_{j=-\infty}^{\infty} \sum_{i=0}^{N_f - 1} P[t - (jN_f + i)T_f] \left| \sum_{k=0}^{M} d_{jk} c_{ik} \right|$$

(3.4)

Where, p(t) is the  $T_P$  duration UWB pulse,  $T_f$  is the time between the pulses,  $N_f$  is the number of frames transmitted,  $c_{ik} \in \{-1,1\}$  is the (M+1) shifting codes as they are denoted in Equation (3.2), and  $d_{jk} \in \{-1,1\}$  is the  $k^{th}$  differentially encoded information bit which is transmitted during the  $j^{th}N_fT_f$  duration [2].

The differentially encoded information bit  $(d_{jk})$  is defined in [2] as:

$$d_{jk} = \begin{cases} \prod_{l=1}^{k} b_{jl} & k = 0, \\ 1 & \forall k \in \{1, 2, \dots, M\}, \end{cases}$$

(3.5)

#### 3.5.2 The Structure of the DCSR-UWB Receiver

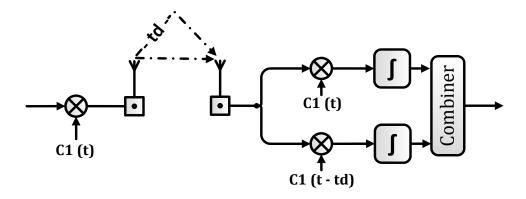

Due to the differentially encoded information bits at the transmitter of the DCSR-UWB system, the structure of the DCSR-UWB receiver differs from the CSR-UWB receiver only in the information bit detection rule. Figure 3.9 shows the proposed structure of the DCSR-UWB receiver [2].

Figure 3.9: The structure of the DCSR-UWB receiver [2]

Figure 3.10: Information bit detection unit of the DCSR-UWB receiver [2]

As in the CSR-UWB receiver, the received signal of the DCSR-UWB system passes through the same front end of the CSR-UWB. First, in order to eliminate the noise and interference, the received signal is passed through a band-pass filter (BPF). Second, a square unit is applied to the filtered signal. Third, in order to obtain  $r_{ij}$ , the squared signal is then integrated from  $(jN_f + i)T_f$  to  $(jN_f + i)T_f + T_M$ . Finally,  $r_{ij}$  is decoded with the detection codes (M(M+1)/2) to obtain  $\tilde{r}_{jln}$  in order to get the original information bits (M) [2].

The information bit detection unit is shown in Figure 3.10 and the detection codes (M(M+1)/2) with  $\tilde{c}_{jln} \in \{-1,1\}$  are defined in [2] as:

$$\begin{bmatrix} \tilde{c}_{01} \\ \vdots \\ \tilde{c}_{0M} \\ \tilde{c}_{12} \\ \vdots \\ \tilde{c}_{1M} \\ \tilde{c}_{23} \\ \vdots \\ \tilde{c}_{(M-1)M} \end{bmatrix} = \begin{bmatrix} \tilde{c}_{001} & \cdots & \tilde{c}_{i01} & \cdots & \tilde{c}_{(N_f-1)01} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ \tilde{c}_{00M} & \cdots & \tilde{c}_{i0M} & \cdots & \tilde{c}_{(N_f-1)0M} \\ \tilde{c}_{012} & \cdots & \tilde{c}_{i12} & \cdots & \tilde{c}_{(N_f-1)12} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ \tilde{c}_{01M} & \cdots & \tilde{c}_{i1M} & \cdots & \tilde{c}_{(N_f-1)1M} \\ \tilde{c}_{023} & \cdots & \tilde{c}_{i23} & \cdots & \tilde{c}_{(N_f-1)23} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ \tilde{c}_{0(M-1)M} & \cdots & \tilde{c}_{i(M-1)M} & \cdots & \tilde{c}_{(N_f-1)(M-1)M} \end{bmatrix}$$

$$(3.6)$$

## 3.5.3 Shifting and Detection Code-Selection for the DCSR-UWB System

The shifting codes and detection codes have been selected from Walsh codes for the sake of detecting the transmitted information bits accurately in the receiver side of the DCSR-UWB system [2]. An example of the selection of the shifting codes and detection codes for the DCSR-UWB system is given in Table 3.2.

Table 3.2: The selection of the shifting and detection codes example for the DCSR-UWB system [2]

| Code<br>Length | Shifting Codes                                                                                                                                                                                           | Detection Codes                                                                                                                                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $N_f = 2$      | $c_0 = [1, 1]$ $c_1 = [1, -1]$                                                                                                                                                                           | $\widetilde{c}_{01} = [1, -1]$                                                                                                                                                                                                                                                                                       |

| $N_f = 4$      | $c_0 = [1,1,1,1]$ $c_1 = [1,-1,1,-1]$ $c_2 = [1,1,-1,-1]$                                                                                                                                                | $\widetilde{c}_{01} = [1, -1, 1, -1]$ $\widetilde{c}_{02} = [1, 1, -1, -1]$ $\widetilde{c}_{12} = [1, -1, -1, 1]$                                                                                                                                                                                                    |

| $N_f = 8$      | $c_0 = [ \ 1 \ , 1 \ , 1 \ , 1 \ , 1 \ , 1 \ , 1 \ ]$ $c_1 = [ \ 1 \ , -1 \ , 1 \ , -1 \ , -1 \ , -1 \ ]$ $c_2 = [ \ 1 \ , 1 \ , -1 \ , -1 \ , -1 \ ]$ $c_3 = [ \ 1 \ , 1 \ , 1 \ , 1 \ , -1 \ , -1 \ ]$ | $\widetilde{c}_{01} = [1, -1, 1, -1, 1, -1, 1, -1]$ $\widetilde{c}_{02} = [1, 1, -1, -1, 1, 1, -1, -1]$ $\widetilde{c}_{03} = [1, 1, 1, 1, -1, -1, -1, -1]$ $\widetilde{c}_{12} = [1, -1, -1, 1, 1, -1, -1, 1]$ $\widetilde{c}_{13} = [1, -1, 1, -1, -1, 1, -1, 1]$ $\widetilde{c}_{23} = [1, 1, -1, -1, -1, -1, 1]$ |

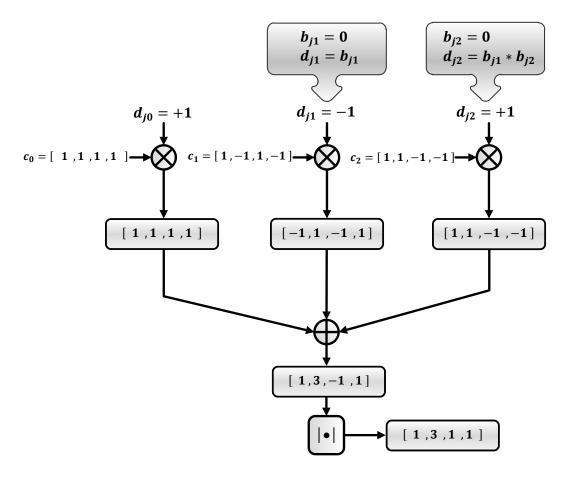

### 3.5.4 DCSR-UWB Encoding Example

If the number of frames  $(N_f)$  is 4, for example, then the number of information bits (M), that can be transmitted, can be determined by:  $M(M+1)/2 \le N_f - 1$ ; therefore, the number of information bits (M) for this example is  $2 (M = 2, N_f = 4)$ . In addition, there will be M+1 orthogonal shifting codes where the length of these codes is equal to  $N_f$ .

As a result, the number of orthogonal shifting codes is going to be 3 and the code length is 4 as it is given in Table 3.3.

Table 3.3: The selection of the shifting and detection codes from Walsh codes when  $N_f = 4$  [2]

| Code<br>Length | Shifting Codes                                                       | Detection Codes                                                                                                   |  |

|----------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| $N_f = 4$      | $c_0 = [ 1, 1, 1, 1 ]$ $c_1 = [1, -1, 1, -1]$ $c_2 = [1, 1, -1, -1]$ | $\widetilde{c}_{01} = [1, -1, 1, -1]$ $\widetilde{c}_{02} = [1, 1, -1, -1]$ $\widetilde{c}_{12} = [1, -1, -1, 1]$ |  |

For the DCSR-UWB system, the original information bits  $(b_{JM})$  should be encoded differentially  $(d_{JM})$  first from Equation (3.5). Consequently, the original information bits  $b_{J1}$  and  $b_{J2}$  are going to be  $d_{j1}$  and  $d_{j2}$ . After the combination of the differential codes with the shifting codes, the amplitudes of the UWB pulses will be determined.

If  $b_{J1} = 0$  and  $b_{J2} = 0$  are chosen for this example, then:

- $d_{J0} = 1$ , which is fixed at (+1) with bipolar expression

- $d_{j1} = b_{J1} = 0$ , which is going to be (-1) with bipolar expression

- $d_{j2} = \overline{b_{J1} * b_{J2}} = 1$ , which is going to be (+1) with bipolar expression

From Table 3.3, the shifting codes are:

- $c_0 = [1, 1, 1, 1]$

- $c_1 = [1, -1, 1, -1]$

- $c_2 = [1, 1, -1, -1]$

As a result, the amplitude values for  $b_{J1} = 0$  and  $b_{J2} = 0$  are (1311) as it is shown in Figure 3.11, and the rest of amplitude pulses are going to be generated using this same procedure.

Figure 3.11: The amplitudes of the UWB pulses when  $b_{J1} = 0$  and  $b_{J2} = 0$

# 3.6 Performance Comparison

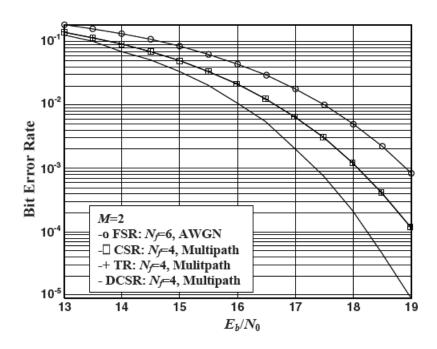

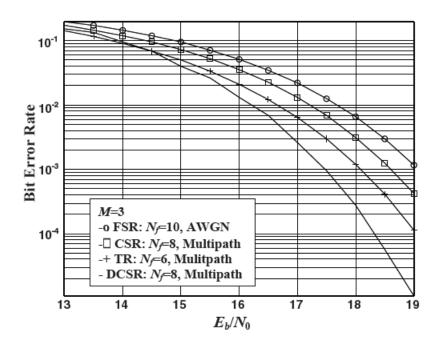

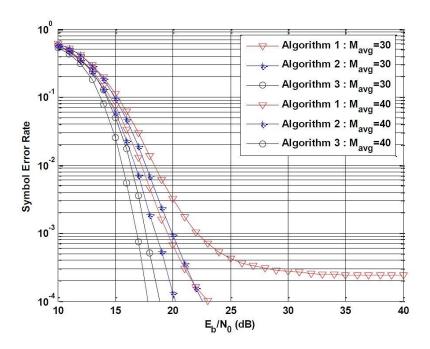

The issues of the TR and FSR schemes were solved by the CSR system since the requirements of the delay elements and the analog carriers are removed. As a result, the system complexity is reduced, and the performance degradation, which takes place in the FSR system, is removed [1]. In [26], the performance of the DCSR compared to other pervious schemes was analysed theoretically as shown in Figure 3.12 and Figure 3.13.

The best BER performance was achieved by the DCSR system among the TR, FSR, and CSR systems since the DCSR has the advantage of high bit-to-pulse ratio and reference power reduction; nevertheless, the FSR system has the worst BER performance where the

BER performance has positive relation with the highest bit-to-pulse ratio  $(M/N_f)$ . The DCSR has the highest or close to highest bit-to-pulse ratio while the highest bit-to-pulse ratio of the FSR system that can be achieved is 1/3. Moreover, The TR and CSR systems spend half of their power transmitting the reference pulses; therefore, the DCSR scheme was proposed to improve the system performance in which the transmitting power is reduced from half to 1/(M+1) [26].

Figure 3.12: BER comparison between DCSR, CSR, FSR and TR, where M=2 [26]

Figure 3.13: BER comparison between DCSR, CSR, FSR and TR, where M=3 [26]

A comparison chart between the TR, FSR, CSR and DCSR systems is given in [26] and it is shown in Table 3.4.

Table 3.4: A comparison chart between the TR, FSR, CSR and DCSR systems [26]

|                  | TR   | FSR   | CSR                 | DCSR                |

|------------------|------|-------|---------------------|---------------------|

| Delay Element    | Yes  | No    | No                  | No                  |

| Analog Carriers  | No   | Yes   | No                  | No                  |

| Reference Power  | 1/2  | 1/2   | 1/2                 | 1/(M+1)             |

| $M/N_f$          | 1/2  | < 1/2 | Up to $\frac{1}{2}$ | Up to $\frac{1}{2}$ |

| Multipath Errors | No   | Yes   | No                  | No                  |

| PAPR             | Low  | High  | Medium              | Medium              |

| Performance      | Good | Poor  | Good                | Best                |

| Complexity       | High | High  | Low                 | Low                 |

# CHAPTER 4: DCSR IR-UWB SYNCHRONIZATION

Synchronization is the adjustment of time to adjust a transmitter and receiver to work in harmony. This adjustment can be described in terms of phase locking and frequency or energy detecting. In this chapter, the synchronization of the DCSR IR-UWB system including the previous timing recovery scheme and code synchronization are discussed after providing the transceiver structure of the DCSR IR-UWB. The limitation of the previous design of the timing recovery and related conclusions are also given.

## 4.1 Introduction

In order to operate a digital transmission system, time synchronization is required between the transmitter and the receiver in which the transmitted information is recovered by synchronization algorithms. In IR-UWB, the system is highly sensitive to timing error due to the ultra-short pulses and the low power of the system [5] [6]. As a result, synchronization is a difficult challenge to the deployment of a UWB system [27] [28]. The performance of the IR-UWB system depends on the timing acquisition; therefore, accurate synchronization has to be achieved [29] [30]. In addition, the synchronization complexity can be affected by the receiver design [31]. These receivers are either coherent receivers, or non-coherent receivers [32] [33].

Coherent receivers were initially proposed for the IR-UWB system, such as the Rake receiver and the matched filter receiver [34] [18]. Coherent correlation receiver demodulates the received signal by correlating it with a designed template signal [32] [35]. In this coherent receiver, defined template signal design and pulse-level synchronization are required where the synchronization is needed to align the received signal with the template signal. Therefore, the performance of the system depends on the synchronization [32] [35]. In addition, complexity of the coherent auto correlation "Rake"

receiver" is high due to the channel estimation, resolvable multipath components, and tracking operation [1] [18] [35].

Non-coherent receivers, however, need less power and do not require channel estimation. Non-coherent receivers catch a large amount of the transmitted energy; as a result, the non-coherent receiver has lower complexity than a coherent receiver [36] [34]. Furthermore, synchronization is required for: First, adjusting the clock of the receiver to synchronize with the clock of the transmitter (timing recovery level) and, second, identifying the first frame of each symbol in the incoming frames (code synchronization level) [32] [34]. In non-coherent receivers, while the received signal acts as the template signal, there is no need for the precise template signal [35]. Since IR-UWB system is highly sensitive to timing error due to the remarkably short pulses and the low power of the system, the system needs high synchronization accuracy; consequently, this leads to high synchronization complexity [32].

Transmitted reference (TR) and differential transmitted reference (DTR) were introduced to overcome the issue of the pulse-detection technique and channel estimation of the coherent receiver. In both the TR and DTR systems, the received modulated data pulse is delayed with a reference pulse and then correlated with each other at the receiver [5] [21] [35]. The slightly frequency-shifted reference (FSR) [22], code-shifted reference (CSR) [1], and differential code-shifted reference (DCSR) [2] were subsequently proposed, as discussed in Chapter 3.

The DCSR IR-UWB transceiver design and synchronization algorithm in the following sections have been proposed by former students in our group research in [3] and [4]. The transceiver structure and synchronization algorithm will be explained in the following subsections.

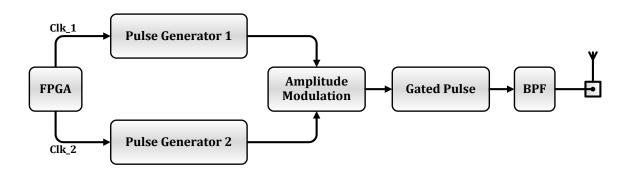

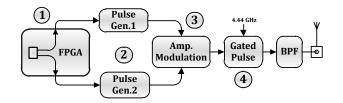

## 4.2 Transmitter Structure of the DCSR IR-UWB

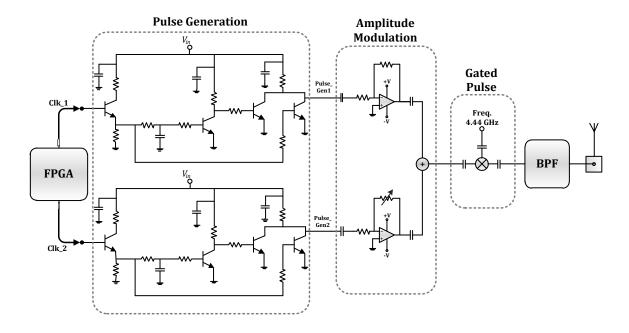

Figure 4.1 illustrates the structure of the DCSR IR-UWB transmitter which consists of three main stages [3]. Pulse generation is the first stage in which it comes after the field programmable gate array (FPGA) as a source for the clocks. In this stage, two identical impulse generators are applied to produce pulses from different clock signals. These pulse generators consist of delay elements and many high speed transistors as shown in Figure 4.2. Second, the amplitude modulation stage modulates the received impulses that are produced by the two pulse generators. The two signals are going to be joined into one signal after the amplitude modulation as it shown in Figure 4.2. Finally, the center frequency of the signal spectrum is controlled by the pulse gating stage. This stage locates the center frequency of the signal spectrum to work under the specified power spectral mask for the UWB communication system that is defined by the FCC. Figure 4.2 shows the three stages of the DCSR IR-UWB transmitter in details.

Figure 4.1: The block diagram of the DCSR IR-UWB transmitter [3] [4]

Figure 4.2: The detailed structure of the DCSR IR-UWB transmitter [3]

# 4.3 Receiver Structure of the DCSR IR-UWB

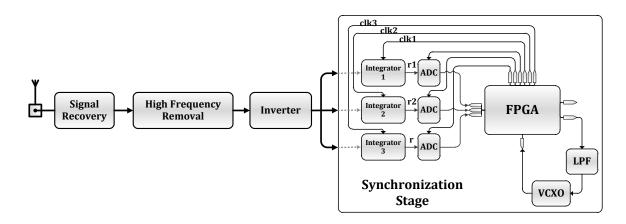

Figure 4.3: Block diagram of the DCSR IR-UWB receiver [3] [4]

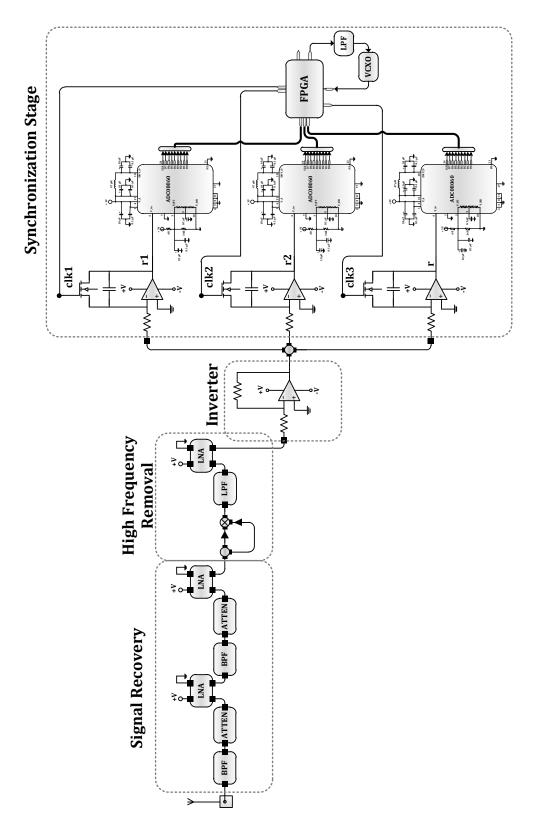

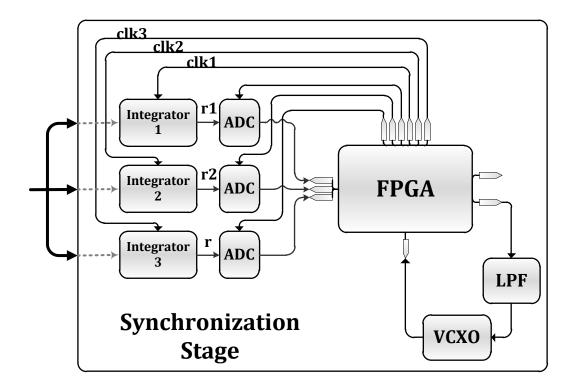

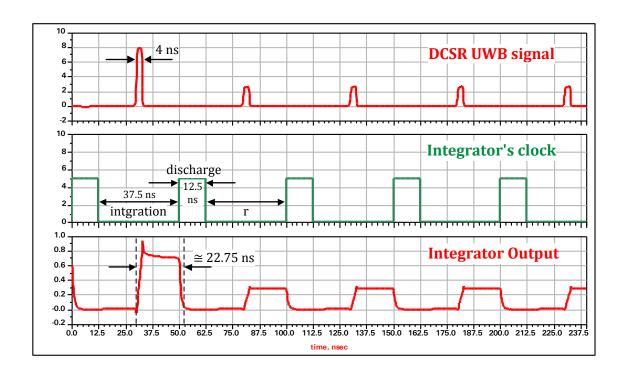

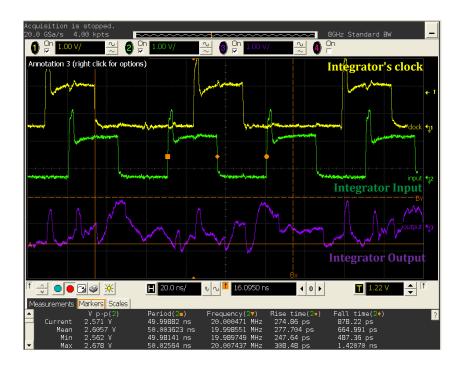

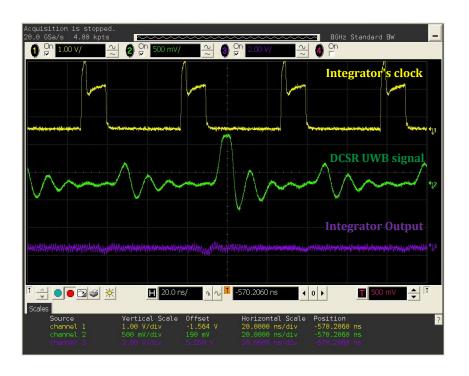

Signal recovery, high frequency removal, inverter, and synchronization are the four main stages for the general structure of the proposed DCSR IR-UWB receiver as it is shown in Figure 4.3 and Figure 4.4 [3] [4]. The signal recovery is the first stage, which involves of two sets of band-pass filters (BPF), a variable attenuator (ATTEN), and low noise amplifier (LNA). In order to recover the received signal, this stage filters and amplifies the received signal, provides high wideband gain, and keeps the noise as minimal as possible. The second stage, the high frequency removal stage, moves the signal back down to the base band from the UWB transmission band. The received signal is squared, filtered, and amplified in this stage in order to remove the high frequency component. The third stage, the inverter stage, is used to cancel the negative polarity of the signal that is going to be produced by the integrators in the synchronization stage. Finally, synchronization between the transmitter and receiver clock is provided by using the concept of the phase-locked loop (PLL) in the final stage. This stage contains three switch-controlled integrators, three analog-to-digital converters (ADCs), a FPGA, a lowpass filter (LPF) and a voltage-controlled crystal oscillator (VCXO). The switchcontrolled integrators detect the pulse energy in different defined times which are controlled by switches. Based on the integration results, the FPGA within the PLL circuit adjusts the receiver clock to be locked to the transmitter clock. After that, the first frame of each symbol in the incoming frames (code synchronization level) needs to be identified before detecting and extracting data from the DCSR decoding pulse sequences.

The process of synchronization of the DCSR IR-UWB system will be described in detail in the following section.

Figure 4.4: The detailed structure of the DCSR IR-UWB receiver [3]

# 4.4 Synchronization of the DCSR IR-UWB

The synchronization stage is an essential subsystem of any communication receiver to coordinate the timing information between the receiver and transmitter. In non-coherent systems, such as the DCSR IR-UWB system, the synchronization is a difficult task due to the short pulses and low duty cycle signaling that is employed in the UWB system. A distorted-transmitted pulse that is caused by the antenna and the channel is also another challenging aspect of the UWB synchronization. In order to provide a low complex receiver in the non-coherent systems, an energy detection technique can be utilized in the synchronization stage. An extracting and decoding process will be started after the timing information is recovered. Therefore, synchronization in the DCSR IR-UWB system is a two part process: The first is to adjust the clock of the receiver to synchronize with the clock of the transmitter (timing recovery level), and the second is identifying the first frame of each symbol in the incoming frames (code synchronization level) in order to apply the detection codes to recover the original information bits. Both the timing recovery and code synchronization levels of the DCSR IR-UWB system will be described in the following subsections.

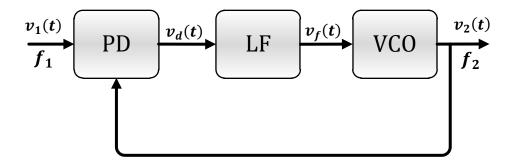

#### 4.4.1 Timing Recovery Level